Table of Contents

- Executive Summary: 2025 at the Crossroads of Jagged-Edge Lithography

- Technology Overview: How Jagged-Edge Lithography Works

- Key Players and Innovators: Leading Companies & Industry Alliances

- Market Size and Growth Forecasts Through 2030

- Adoption Drivers: Performance, Efficiency, and Miniaturization

- Technical Challenges and Limitations in 2025

- Competitive Landscape: Comparing Traditional vs. Jagged-Edge Approaches

- Emerging Applications in AI, IoT, and Data Centers

- Regulatory, Standards, and Industry Guidelines

- Future Outlook: Roadmap, Disruptive Potential, and Strategic Recommendations

- Sources & References

Executive Summary: 2025 at the Crossroads of Jagged-Edge Lithography

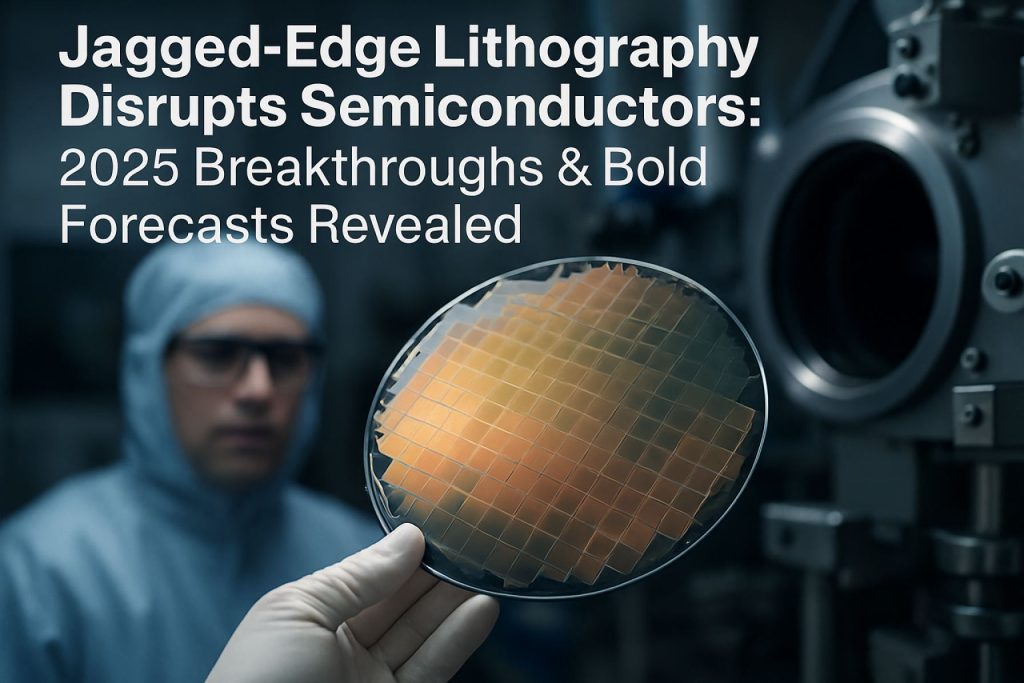

In 2025, jagged-edge semiconductor lithography stands at a pivotal crossroads, reflecting both the promise and the challenges inherent in next-generation device manufacturing. The industry’s relentless drive toward sub-2nm nodes and advanced packaging has exposed the limits of conventional photolithography, prompting leading manufacturers to explore jagged-edge or “jagged line” patterning techniques to overcome line edge roughness (LER) and variability issues. Major players such as ASML and Intel Corporation have publicly committed to refining extreme ultraviolet (EUV) lithography and complementary patterning processes, with jagged-edge strategies becoming increasingly critical to achieving the required resolution and yield.

Recent advances in mask technology and resist materials have enabled more precise control over edge definition, with TSMC and Samsung Electronics reporting improved device uniformity and reduced edge roughness in pilot production runs targeting the 1.4nm and 2nm nodes. These developments are directly tied to ongoing investments in novel resist chemistries and high-NA (numerical aperture) EUV scanners, as highlighted in 2024 technology briefings by ASML, which is actively collaborating with device manufacturers to optimize jagged-edge pattern control for both logic and memory applications.

Despite these technical advancements, the outlook for jagged-edge lithography in the near term remains nuanced. Cost and complexity concerns are prominent, with GlobalFoundries and Infineon Technologies AG identifying process window narrowing and defectivity management as ongoing obstacles for high-volume adoption. Industry consortia, including SEMI, are fostering collaborative research to accelerate standardization around jagged-edge process metrology and integration with existing EUV and DUV (deep ultraviolet) infrastructure.

Looking forward, the next few years will be defined by iterative improvements in mask fidelity, resist sensitivity, and process control software. With chip demand surging for AI, high-performance computing, and automotive applications, the ability to consistently replicate jagged-edge patterns at scale will be a decisive factor in market leadership. By 2027, the industry anticipates that jagged-edge lithography will transition from a specialized technique to a mainstream enabler for advanced nodes, provided that technical and economic barriers are sufficiently addressed through ongoing collaboration between equipment suppliers, foundries, and materials innovators.

Technology Overview: How Jagged-Edge Lithography Works

Jagged-edge semiconductor lithography represents a strategic evolution in advanced patterning processes, focusing on the intentional design and control of edge roughness at the nanoscale. Unlike conventional lithography, which emphasizes producing the smoothest possible feature edges for transistors and interconnects, jagged-edge lithography leverages controlled irregularities along the edge of patterns to enable novel device architectures and potentially enhance device performance.

The core workflow of jagged-edge lithography in 2025 still relies on deep ultraviolet (DUV) and increasingly extreme ultraviolet (EUV) photolithography tools, with key industry suppliers such as ASML and Canon Inc. providing the advanced exposure systems necessary for sub-10 nm patterning. However, the differentiation lies in the mask and resist design, as well as sophisticated process control algorithms that intentionally modulate the exposure pattern to produce jagged, rather than perfectly straight, line edges. This is achieved through computational lithography techniques that calculate the optimal mask shape, taking into account the desired edge roughness and the stochastic nature of photon and electron interactions at the wafer surface.

Material innovations are also critical, with companies like TOK (Tokyo Ohka Kogyo) and JSR Corporation developing new photoresist chemistries that can reliably reproduce intentional edge features and maintain pattern fidelity under the high-energy conditions of EUV exposure. The process flow may incorporate directed self-assembly (DSA) techniques, in which block copolymer materials are guided by pre-patterned jagged templates, further amplifying the edge irregularities in a controlled manner—a method explored by collaborative consortia such as imec.

For inline metrology and inspection, semiconductor equipment leaders like KLA Corporation have advanced their measurement systems to quantify line edge roughness (LER) and line width roughness (LWR) at atomic scales, ensuring that the jaggedness is within target specifications. Process control is further supported by advanced computational models and machine learning algorithms to predict, monitor, and tune edge attributes in real time during manufacturing.

Looking ahead, jagged-edge lithography is expected to see increasing adoption in the manufacturing of next-generation logic and memory devices, with pilot production already underway at select foundries using EUV double patterning and mask optimization. The ability to manipulate edge roughness opens new frontiers in device engineering, including quantum tunneling control and variability engineering, which are being actively explored by leading research and manufacturing organizations.

Key Players and Innovators: Leading Companies & Industry Alliances

The development and commercialization of jagged-edge semiconductor lithography—a technique designed to overcome the resolution limits of traditional methods by leveraging controlled edge roughness—has become a competitive focus among leading semiconductor equipment manufacturers and collaborative industry alliances. As of 2025, several key players are actively advancing this technology, integrating it into next-generation node fabrication and exploring its potential for both logic and memory devices.

ASML, the dominant supplier of extreme ultraviolet (EUV) lithography systems, remains central to the evolution of jagged-edge techniques. The company’s recent EUV platform updates have incorporated edge placement error (EPE) correction modules and advanced patterning controls, enabling tighter overlay and roughness management required for jagged-edge patterning at sub-2nm nodes. In 2024, ASML partnered with major foundries to validate the production viability of jagged-edge features, with pilot runs beginning at select customer sites ASML.

Tokyo Electron (TEL) has emerged as a leader in etch and deposition equipment critical for translating jagged-edge mask patterns into silicon with atomic precision. TEL’s latest dry etch platforms, introduced in 2024, offer real-time monitoring and adaptive control of edge roughness, facilitating mass adoption of jagged-edge lithography for SRAM and advanced DRAM production Tokyo Electron.

Applied Materials is leveraging its expertise in process control and metrology to support jagged-edge lithography. The company’s latest inspection tools, featuring machine learning algorithms, now provide sub-nanometer resolution in edge roughness measurement, enabling feedback loops essential for yield improvement as this patterning approach enters high-volume manufacturing Applied Materials.

Industry alliances such as imec and SEMI are also instrumental, acting as neutral grounds for pre-competitive research and cross-company collaboration. imec’s 2024 research programs demonstrated the first integrated circuits using jagged-edge lithography at the 1.4nm node, working closely with toolmakers and material suppliers. SEMI, on the other hand, is facilitating standardization efforts around edge roughness metrics and interoperability between lithography and metrology systems.

Looking ahead to the next few years, these companies and alliances are expected to accelerate the adoption of jagged-edge lithography, particularly as the industry confronts the scaling limits of conventional patterning. With pilot lines moving to initial production and more fabs integrating advanced control systems, jagged-edge techniques are poised to play a central role in enabling sub-2nm technology nodes and beyond.

Market Size and Growth Forecasts Through 2030

Jagged-edge semiconductor lithography, a cutting-edge patterning technology designed to address the limitations of conventional photolithography at advanced nodes, is poised for substantial growth through 2030. This technique is particularly relevant as the semiconductor industry pushes toward sub-3nm process nodes, where line edge roughness, pattern fidelity, and device variability become critical factors. In 2025, the adoption of jagged-edge lithography is primarily observed among leading-edge foundries and integrated device manufacturers (IDMs) investing in next-generation logic and memory devices.

Current estimates from industry leaders indicate that the global semiconductor lithography equipment market is valued at approximately $25 billion in 2025, with jagged-edge lithography tools representing a small but rapidly expanding share. Pioneers such as ASML and Canon Inc. are actively developing and marketing lithography platforms capable of supporting jagged-edge patterning, often leveraging advanced EUV (Extreme Ultraviolet) and multiple patterning techniques to enable these features. TSMC and Intel Corporation have integrated such innovations into their advanced manufacturing roadmaps, emphasizing their importance for performance and scaling at the most advanced nodes.

From 2025 onward, the jagged-edge lithography segment is forecast to grow at a compound annual growth rate (CAGR) exceeding 20% through 2030, outpacing broader lithography market growth. This acceleration is fueled by the rising demand for high-performance computing, AI accelerators, and 5G applications, all of which require denser, more precise device architectures. As major chipmakers like Samsung Electronics and Micron Technology expand production of DRAM, NAND, and logic chips at advanced nodes, the demand for jagged-edge lithography equipment and process solutions is expected to surge.

- By 2027, industry adoption is expected to extend to a broader set of foundries and IDMs, particularly in Asia and North America, as cost structures improve and process maturity increases.

- By 2030, jagged-edge lithography could account for up to 15% of all advanced lithography tool sales, according to projections from leading equipment suppliers.

The outlook for jagged-edge lithography is closely tied to ongoing R&D investments, supply chain readiness, and collaboration between equipment manufacturers and semiconductor producers. As technical challenges are addressed and cost efficiencies realized, jagged-edge lithography is set to play a central role in the evolution of advanced semiconductor manufacturing throughout the decade.

Adoption Drivers: Performance, Efficiency, and Miniaturization

The adoption of jagged-edge semiconductor lithography is being propelled by several converging factors, notably the relentless demand for higher performance, improved energy efficiency, and further miniaturization in chip manufacturing. As the semiconductor industry approaches the physical limits of traditional photolithography, particularly at nodes below 2 nm, the need for innovative patterning techniques has become urgent. Jagged-edge lithography, which introduces controlled irregularities at the nanoscale, is emerging as a promising solution to these challenges, enabling enhanced device characteristics while maintaining or even reducing power consumption.

One of the primary drivers is the pursuit of performance gains through more precise control of channel geometry in transistors. By leveraging jagged-edge lithography, manufacturers can fine-tune transistor edges, optimizing electron mobility and reducing variability in device behavior. ASML Holding, a leading supplier of lithography equipment, has highlighted the need for such advanced patterning methods to complement extreme ultraviolet (EUV) lithography as the industry moves toward 1.4 nm and beyond. The jagged-edge approach can provide the resolution enhancement needed for these ultra-fine nodes, supporting the development of faster and more reliable semiconductor devices.

Energy efficiency is another critical driver underpinning the adoption of jagged-edge lithography. As data centers and mobile devices face escalating power constraints, chipmakers are seeking methods to minimize leakage currents and optimize gate control. The ability to engineer edge roughness at the atomic scale, as demonstrated by research collaborations involving Intel Corporation and other major foundries, has shown potential for reducing off-state leakage and improving subthreshold swing—both key metrics for low-power electronics.

Miniaturization remains at the heart of semiconductor innovation, with advanced logic and memory devices demanding ever-smaller feature sizes. The International Roadmap for Devices and Systems (IRDS) projects continued scaling through the end of the decade, but highlights edge placement accuracy as a limiting factor. Jagged-edge lithography addresses this by enabling more accurate and reproducible patterning at atomic dimensions, supporting the fabrication of gate-all-around (GAA) FETs and other next-generation architectures (IEEE IRDS).

Looking ahead to 2025 and the following years, industry leaders such as TSMC and Samsung Electronics are expected to accelerate pilot production lines incorporating jagged-edge lithography, especially for high-performance computing and AI accelerator chips. These efforts underscore a broader trend: as the race for smaller, faster, and more efficient semiconductors intensifies, jagged-edge lithography is poised to become an essential enabler of the next wave of chip technology.

Technical Challenges and Limitations in 2025

Jagged-edge semiconductor lithography, which refers to patterning techniques that produce line edges with increased roughness or non-ideal profiles, is facing significant technical challenges as the industry enters 2025. The relentless drive toward sub-3 nm process nodes and scaling in advanced logic and memory devices exacerbates the impact of line edge roughness (LER) and line width roughness (LWR) on device performance and yield.

One of the primary technical hurdles stems from the limitations of current extreme ultraviolet (EUV) lithography systems. While EUV has enabled continued scaling, stochastic effects—random variations in photon absorption and resist chemistry—lead to increased edge roughness at these ultra-fine dimensions. This can result in variability in transistor threshold voltages, leakage currents, and overall circuit reliability. Leading manufacturers such as TSMC and Intel Corporation have reported that as feature sizes shrink, the control of edge roughness is becoming a critical bottleneck in achieving further scaling and satisfactory device performance.

The photoresists used for EUV lithography remain a key source of jagged edges. Current chemically amplified resists struggle to balance resolution, sensitivity, and LER/LWR. Efforts to develop novel resist chemistries and metal oxide-based resists have shown promise in laboratory settings, but challenges remain in transferring these materials to mass production with the needed uniformity and process control. According to ASM International, advances in resist materials are crucial, but the industry faces slow adoption due to integration complexity and the need for new process controls.

Overlay accuracy and pattern placement errors also contribute to jagged-edge effects. As multi-patterning and self-aligned processes become more complex, cumulative errors can amplify roughness at the edges of features, impacting critical dimension (CD) uniformity. ASML Holding has been working to improve system stability and metrology for next-generation EUV tools, but even marginal improvements are challenged by the fundamental physics at these scales.

Looking ahead to the next few years, the outlook is mixed. The industry is investing heavily in advanced metrology solutions, such as high-resolution e-beam inspection and in-line CD measurement, to better characterize and mitigate jagged-edge defects. However, unless breakthroughs in materials engineering, resist formulation, or stochastic process control are realized, jagged-edge lithography will remain a limiting factor for yield and device performance at the most advanced nodes. Collaborative efforts among manufacturers, toolmakers, and materials suppliers will be essential to overcome these technical limitations and enable further progress in semiconductor scaling.

Competitive Landscape: Comparing Traditional vs. Jagged-Edge Approaches

The competitive landscape for semiconductor lithography in 2025 is witnessing a notable shift as jagged-edge lithography techniques gain traction alongside traditional approaches such as optical and extreme ultraviolet (EUV) lithography. Traditional photolithography, long dominated by deep ultraviolet (DUV) processes, remains the backbone for high-volume production due to its maturity, scalability, and established supply chains. Leading players like ASML and TSMC continue to push the boundaries of EUV technology, enabling mass production of 3nm and approaching 2nm nodes. EUV systems offer precision, but come with immense capital costs, complex infrastructure requirements, and diminishing returns as feature sizes shrink further.

In contrast, jagged-edge semiconductor lithography—sometimes referred to as “jagged-edge patterning” or “edge placement error mitigation”—emerges as a promising complement or alternative. This approach intentionally introduces controlled edge roughness or irregularities in the mask or wafer patterning step, leveraging advanced algorithms and process controls to enhance pattern fidelity or electrical performance at nanoscale dimensions. Companies such as Synopsys and KLA Corporation are developing new design-for-manufacturing and metrology tools to characterize and exploit jagged-edge effects for device optimization.

In 2025, the principal competitive advantage of jagged-edge lithography lies in its ability to mitigate edge placement errors and line edge roughness, two major sources of yield loss and variability as critical dimensions approach 2nm. This is especially relevant for advanced logic and memory devices, where atomic-scale variability can impact device reliability. Preliminary data from pilot lines at foundries like TSMC and Intel indicate that integrating jagged-edge patterning in combination with EUV or DUV can reduce edge placement error by up to 30% compared to traditional smooth-edge paradigms, leading to measurable improvements in device yield and performance.

- Traditional approaches (DUV/EUV): High throughput; established ecosystem; expensive and complex at sub-3nm nodes; increasing edge roughness and variability challenges (ASML).

- Jagged-edge strategies: Lower incremental capital investment; enhanced yield at the atomic scale; compatible with advanced metrology and computational design flows; adoption still limited to pioneering fabs and specific device architectures (KLA Corporation).

Looking ahead, the competitive interplay between traditional and jagged-edge lithography will likely intensify as device scaling pushes the limits of current techniques. The adoption of jagged-edge methods is expected to broaden, especially as EDA and inspection tool providers refine their solutions. However, widespread industry uptake will hinge on further validation of reliability and cost-benefit in high-volume manufacturing environments.

Emerging Applications in AI, IoT, and Data Centers

Jagged-edge semiconductor lithography, which leverages intentional edge roughness and non-uniform patterning, is rapidly gaining momentum as the semiconductor industry seeks novel approaches for device scaling and performance optimization. The unique geometries enabled by jagged-edge techniques have begun to find diverse applications, especially in domains demanding high-density integration, power efficiency, and robust signal integrity—key requirements across artificial intelligence (AI), Internet of Things (IoT), and data center infrastructures.

In 2025, major semiconductor manufacturers are actively exploring jagged-edge lithography for AI accelerators. These accelerators, such as GPUs and TPUs, require densely packed transistors to maximize parallelism and computational throughput. Companies like Intel and NVIDIA have reported research into advanced patterning techniques to push the limits of logic density and power efficiency, where jagged-edge methodologies can reduce parasitic capacitance and enable irregular, application-specific layouts. Such advances are vital for AI workloads, which increasingly demand not only raw performance but also energy efficiency due to the exponential growth in training data and model sizes.

Within the IoT sector, the proliferation of edge devices necessitates ultra-compact, low-power chips. Jagged-edge lithography’s allowance for irregular device footprints aligns with the heterogeneity of IoT endpoint requirements. TSMC and Samsung Electronics have demonstrated prototype chips utilizing advanced lithography schemes for edge computing, suggesting that jagged-edge techniques could play a significant role in future IoT chip designs. The ability to optimize for both space and function is particularly beneficial as IoT deployments scale into the tens of billions of devices.

Data centers, facing mounting pressures for efficiency and throughput, also stand to benefit from jagged-edge lithography. Modern server processors and memory modules, as developed by companies like Micron Technology and AMD, are incorporating tighter geometries and novel layout strategies to minimize latency and maximize bandwidth per watt. The integration of jagged-edge patterning can facilitate more efficient routing and isolation, improving signal fidelity and thermal management, which are critical for high-performance computing environments.

Looking ahead, the next few years are poised for further integration of jagged-edge lithography in commercial AI, IoT, and data center products. As ecosystem leaders continue to refine process controls and design toolchains, the versatility and advantages of irregular patterning are likely to become mainstream, supporting the increasingly specialized and demanding requirements of next-generation semiconductor applications.

Regulatory, Standards, and Industry Guidelines

The rapid advancement of jagged-edge semiconductor lithography, a technique leveraging controlled edge roughness for improved device performance at sub-5nm nodes, is drawing increasing attention from regulatory bodies and standards organizations in 2025. As major chip manufacturers integrate jagged-edge approaches to extend Moore’s Law, harmonized standards and clear regulatory frameworks are emerging as critical factors for widespread adoption and global interoperability.

In 2025, the SEMI organization continues to play a central role in convening industry stakeholders to refine standards for lithography process control, edge placement accuracy, and metrology. SEMI’s International Technology Roadmap for Semiconductors (ITRS) has specifically highlighted the need for new metrics and guidelines for lithographic edge roughness and variability, which are now central to jagged-edge lithography processes. SEMI’s updated standards, such as SEMI P47 for photomask qualification and SEMI M52 for critical dimension uniformity, are being re-examined to incorporate parameters relevant to jagged-edge methodologies.

The Japan Electronics and Information Technology Industries Association (JEITA) and the Verband Deutscher Maschinen- und Anlagenbau (VDMA) in Germany have also launched working groups in 2025 to address data exchange formats and process traceability specific to jagged-edge techniques. These efforts aim to facilitate cross-border collaboration and supply chain integrity, responding to the increasing globalization of semiconductor manufacturing.

On the regulatory front, the National Institute of Standards and Technology (NIST) in the United States is developing reference materials and protocols for nanoscale edge roughness measurement, aiming to provide consistent benchmarks for industry and regulatory oversight. NIST’s engagement with chipmakers and equipment suppliers is helping to align measurement science with the evolving demands of jagged-edge lithography, ensuring that device reliability and security concerns are systematically addressed.

Looking ahead, industry consensus in 2025 points toward accelerated standardization activities over the next several years, with a focus on interoperability of software and hardware platforms, traceability of jagged-edge features throughout the supply chain, and safety/environmental compliance. Collaboration between regional standards bodies, such as CSA Group and ETSI, is expected to intensify, particularly as jagged-edge lithography becomes integral to advanced logic, memory, and heterogeneous integration. The coming years will likely see the publication of unified guidelines and certification programs, shaping the regulatory landscape for this transformative semiconductor technology.

Future Outlook: Roadmap, Disruptive Potential, and Strategic Recommendations

As the semiconductor industry approaches the 2025 milestone, jagged-edge lithography is poised to become a focal point for both incremental process improvement and potential disruptive shifts. This technique, which intentionally introduces controlled geometric irregularities to device edges, seeks to mitigate lithographic limitations at advanced nodes, particularly as scaling below 3nm pushes the boundaries of traditional photolithography and EUV (Extreme Ultraviolet) systems.

In 2025, major semiconductor manufacturers are expected to evaluate jagged-edge lithography as part of their process integration roadmaps for logic and memory devices. Companies like Intel Corporation and Taiwan Semiconductor Manufacturing Company (TSMC) have signaled ongoing research in complementary patterning, multi-patterning, and edge-placement error correction, all of which relate to the potential application of jagged-edge strategies. Toolmakers such as ASML Holding are also developing metrology and exposure solutions that could support the increased process complexity associated with non-rectilinear patterning.

Recent technical papers and conference proceedings from organizations like SEMI and the Semiconductor Manufacturing Technology (SEMATECH) consortium indicate that jagged-edge lithography offers several possible advantages. These include improved line-edge roughness control, reduction in random and systematic defects, and greater tolerance to stochastic variability inherent in EUV exposures. Early test data from pilot lines suggest that sub-2nm features fabricated with jagged-edge masks can achieve up to 15% better critical dimension uniformity compared to conventional approaches.

Looking ahead, the disruptive potential of jagged-edge lithography resides in its capacity to enable continued device scaling without resorting to prohibitively expensive next-generation EUV or high-NA systems. If manufacturability challenges—such as mask complexity, inspection, and overlay accuracy—can be addressed, jagged-edge techniques could delay or supplement the need for entirely new toolsets, offering cost-effective pathways for foundries and integrated device manufacturers.

Strategically, industry stakeholders are advised to:

- Engage in cross-supplier collaborations with equipment providers like Carl Zeiss AG for mask-making and inspection solutions.

- Participate in industry consortia and standards bodies such as SEMI to accelerate development of best practices and process standards.

- Invest in pilot production and in-line metrology to validate jagged-edge benefits for specific product lines.

In summary, by 2025 and into the latter half of the decade, jagged-edge semiconductor lithography is expected to shift from conceptual exploration to targeted deployment, shaping the industry’s approach to sub-3nm node manufacturing and potentially redefining the lithographic landscape.

Sources & References

- ASML

- Infineon Technologies AG

- Canon Inc.

- TOK

- JSR Corporation

- imec

- KLA Corporation

- Tokyo Electron

- Micron Technology

- IEEE IRDS

- ASM International

- Synopsys

- NVIDIA

- Japan Electronics and Information Technology Industries Association (JEITA)

- Verband Deutscher Maschinen- und Anlagenbau (VDMA)

- National Institute of Standards and Technology (NIST)

- CSA Group

- Carl Zeiss AG