Sumário

- Resumo Executivo: 2025 no Cruzamento da Litografia de Borda Irregular

- Visão Geral da Tecnologia: Como Funciona a Litografia de Borda Irregular

- Principais Players e Inovadores: Empresas Líderes & Alianças da Indústria

- Tamanho do Mercado e Previsões de Crescimento Até 2030

- Fatores de Adoção: Desempenho, Eficiência e Miniaturização

- Desafios Técnicos e Limitações em 2025

- Cenário Competitivo: Comparando Abordagens Tradicionais vs. de Borda Irregular

- Aplicações Emergentes em IA, IoT e Centros de Dados

- Regulamentações, Normas e Diretrizes da Indústria

- Perspectivas Futuras: Roteiro, Potencial Disruptivo e Recomendações Estratégicas

- Fontes & Referências

Resumo Executivo: 2025 no Cruzamento da Litografia de Borda Irregular

Em 2025, a litografia de semicondutores de borda irregular se encontra em um ponto crucial, refletindo tanto a promessa quanto os desafios inerentes à fabricação de dispositivos de próxima geração. O impulso incessante da indústria em direção a nós de sub-2nm e embalagens avançadas expôs os limites da fotolitografia convencional, levando os principais fabricantes a explorar técnicas de padronização de borda irregular ou “linha irregular” para superar problemas de rugosidade da borda (LER) e variabilidade. Principais players como ASML e Intel Corporation se comprometeram publicamente a refinar a litografia de ultravioleta extremo (EUV) e processos de padronização complementares, com estratégias de borda irregular tornando-se cada vez mais críticas para alcançar a resolução e o rendimento necessários.

Avanços recentes na tecnologia de máscaras e materiais de resistência permitiram um controle mais preciso sobre a definição da borda, com a TSMC e a Samsung Electronics relatando melhor uniformidade dos dispositivos e redução da rugosidade da borda em execuções de produção piloto visando os nós de 1,4nm e 2nm. Esses desenvolvimentos estão diretamente ligados a investimentos contínuos em quimioterapia nova de resistência e scanners EUV de alta-NA (aperture numérica), como destacado nas informações técnicas de 2024 da ASML, que está colaborando ativamente com fabricantes de dispositivos para otimizar o controle de padronização de borda irregular para aplicações de lógica e memória.

Apesar desses avanços técnicos, a perspectiva para a litografia de borda irregular no curto prazo permanece sutil. Preocupações sobre custo e complexidade são proeminentes, com a GlobalFoundries e a Infineon Technologies AG identificando o estreitamento da janela de processo e a gestão de defeitos como obstáculos contínuos para a adoção em alto volume. Consórcios da indústria, incluindo SEMI, estão promovendo pesquisas colaborativas para acelerar a padronização em torno da metrologia de processos de borda irregular e a integração com a infraestrutura existente de EUV e DUV (ultravioleta profundo).

Olhando para o futuro, os próximos anos serão definidos por melhorias iterativas na fidelidade da máscara, sensibilidade da resistência e software de controle de processos. Com a demanda por chips disparando para aplicações de IA, computação de alto desempenho e automotivas, a capacidade de replicar consistentemente padrões de borda irregular em escala será um fator decisivo na liderança do mercado. Até 2027, a indústria antecipa que a litografia de borda irregular fará a transição de uma técnica especializada para um facilitador comum para nós avançados, desde que as barreiras técnicas e econômicas sejam suficientemente abordadas por meio da colaboração contínua entre fornecedores de equipamentos, fundições e inovadores de materiais.

Visão Geral da Tecnologia: Como Funciona a Litografia de Borda Irregular

A litografia de semicondutores de borda irregular representa uma evolução estratégica nos processos de padronização avançada, focando no design intencional e controle da rugosidade da borda em escala nanométrica. Diferente da litografia convencional, que enfatiza a produção das bordas de recursos mais suaves possíveis para transistores e interconexões, a litografia de borda irregular aproveita irregularidades controladas ao longo da borda dos padrões para permitir novas arquiteturas de dispositivos e potencialmente melhorar o desempenho do dispositivo.

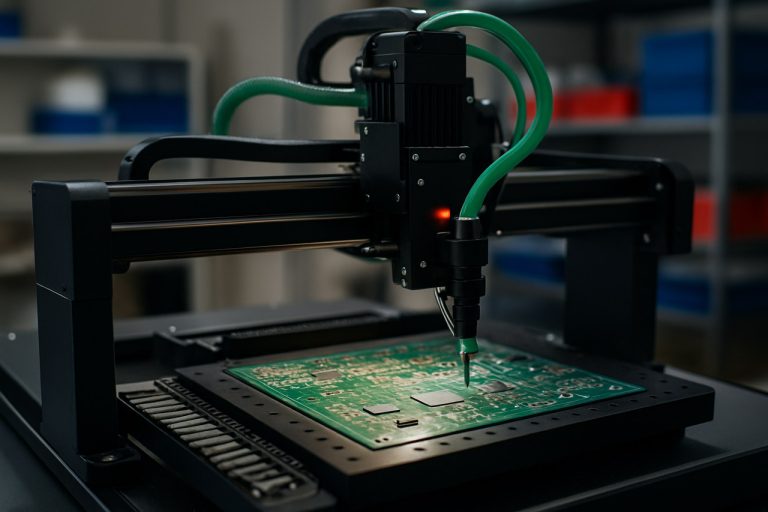

O fluxo de trabalho central da litografia de borda irregular em 2025 ainda depende de ferramentas de fotolitografia ultravioleta profunda (DUV) e cada vez mais de ultravioleta extremo (EUV), com fornecedores-chave da indústria como ASML e Canon Inc. fornecendo os sistemas de exposição avançados necessários para a padronização sub-10 nm. No entanto, a diferenciação está no design da máscara e da resistência, bem como em algoritmos de controle de processos sofisticados que modulam intencionalmente o padrão de exposição para produzir bordas de linha irregulares, em vez de perfeitamente retas. Isso é alcançado por meio de técnicas de litografia computacional que calculam a forma ideal da máscara, levando em conta a rugosidade da borda desejada e a natureza estocástica das interações de fótons e elétrons na superfície do wafer.

Inovações materiais também são críticas, com empresas como TOK (Tokyo Ohka Kogyo) e JSR Corporation desenvolvendo novas químicas de fotoresistência que podem reproduzir com confiabilidade características de borda intencionais e manter a fidelidade do padrão sob as condições de alta energia da exposição EUV. O fluxo do processo pode incorporar técnicas de auto-organização direcionada (DSA), nas quais materiais de copolímero bloqueado são guiados por templates irregulares pré-padronizados, amplificando ainda mais as irregularidades da borda de forma controlada—um método explorado por consórcios colaborativos como imec.

Para metrologia e inspeção em linha, líderes em equipamentos semicondutores como KLA Corporation avançaram seus sistemas de medição para quantificar a rugosidade da borda da linha (LER) e a rugosidade da largura da linha (LWR) em escalas atômicas, garantindo que a irregularidade esteja dentro das especificações alvo. O controle do processo é ainda apoiado por modelos computacionais avançados e algoritmos de aprendizado de máquina para prever, monitorar e ajustar atributos de borda em tempo real durante a fabricação.

Olhando adiante, espera-se que a litografia de borda irregular veja uma adoção crescente na fabricação de dispositivos de lógica e memória de próxima geração, com produção piloto já em andamento em algumas fundições usando padronização dupla EUV e otimização de máscara. A capacidade de manipular a rugosidade da borda abre novas fronteiras na engenharia de dispositivos, incluindo controle de tunelamento quântico e engenharia de variabilidade, que estão sendo ativamente exploradas por organizações de pesquisa e fabricação líderes.

Principais Players e Inovadores: Empresas Líderes & Alianças da Indústria

O desenvolvimento e a comercialização da litografia de semicondutores de borda irregular—uma técnica projetada para superar os limites de resolução dos métodos tradicionais, aproveitando a rugosidade controlada da borda—tornou-se um foco competitivo entre os principais fabricantes de equipamentos semicondutores e alianças colaborativas da indústria. Em 2025, vários players-chave estão ativamente promovendo essa tecnologia, integrando-a à fabricação de nós de próxima geração e explorando seu potencial para dispositivos de lógica e memória.

ASML, o fornecedor dominante de sistemas de litografia de ultravioleta extremo (EUV), continua sendo central para a evolução das técnicas de borda irregular. As atualizações recentes da plataforma EUV da empresa incorporaram módulos de correção de erro de posicionamento de borda (EPE) e controles de padronização avançados, permitindo uma gestão mais rigorosa da sobreposição e rugosidade necessária para a padronização de borda irregular em nós sub-2nm. Em 2024, a ASML se juntou a grandes fundições para validar a viabilidade de produção de características de borda irregular, com execuções piloto começando em sites de clientes selecionados ASML.

Tokyo Electron (TEL) emergiu como um líder em equipamentos de gravação e deposição críticos para traduzir padrões de máscara de borda irregular em silício com precisão atômica. As plataformas de gravação a seco mais recentes da TEL, introduzidas em 2024, oferecem monitoramento em tempo real e controle adaptativo da rugosidade da borda, facilitando a adoção em massa da litografia de borda irregular para a produção de SRAM e DRAM avançado Tokyo Electron.

Applied Materials está aproveitando sua experiência em controle de processos e metrologia para apoiar a litografia de borda irregular. As ferramentas de inspeção mais recentes da empresa, com algoritmos de aprendizado de máquina, agora fornecem resolução subnanométrica na medição da rugosidade da borda, permitindo ciclos de feedback essenciais para a melhoria do rendimento à medida que essa abordagem de padronização entra na fabricação em alto volume Applied Materials.

Alianças da indústria, como imec e SEMI, também são instrumentais, atuando como campos neutros para pesquisa pré-competitiva e colaboração entre empresas. Os programas de pesquisa de 2024 da imec demonstraram o primeiro circuito integrado usando litografia de borda irregular no nó de 1,4nm, trabalhando em estreita colaboração com fabricantes de ferramentas e fornecedores de materiais. A SEMI, por sua vez, está facilitando esforços de padronização em torno de métricas de rugosidade da borda e interoperabilidade entre sistemas de litografia e metrologia.

Olhando para os próximos anos, espera-se que essas empresas e alianças acelerem a adoção da litografia de borda irregular, especialmente à medida que a indústria enfrenta os limites de escalonamento da padronização convencional. Com linhas piloto se movendo para a produção inicial e mais fábricas integrando sistemas de controle avançados, as técnicas de borda irregular estão prontas para desempenhar um papel central na habilitação de nós de tecnologia sub-2nm e além.

Tamanho do Mercado e Previsões de Crescimento Até 2030

A litografia de semicondutores de borda irregular, uma tecnologia de padronização de ponta projetada para abordar as limitações da fotolitografia convencional em nós avançados, está pronta para um crescimento substancial até 2030. Essa técnica é particularmente relevante à medida que a indústria de semicondutores avança em direção a nós de processo sub-3nm, onde a rugosidade da borda, a fidelidade do padrão e a variabilidade do dispositivo se tornam fatores críticos. Em 2025, a adoção da litografia de borda irregular é observada principalmente entre fundições de ponta e fabricantes de dispositivos integrados (IDMs) investindo em dispositivos de lógica e memória de próxima geração.

Estimativas atuais de líderes da indústria indicam que o mercado global de equipamentos de litografia semicondutores está avaliado em aproximadamente $25 bilhões em 2025, com ferramentas de litografia de borda irregular representando uma parte pequena, mas em rápida expansão. Pioneiros como ASML e Canon Inc. estão desenvolvendo ativamente e comercializando plataformas de litografia capazes de suportar a padronização de borda irregular, muitas vezes aproveitando técnicas avançadas de EUV (Ultravioleta Extremo) e múltiplas padronizações para viabilizar essas características. A TSMC e a Intel Corporation integraram tais inovações em seus roteiros de fabricação avançada, enfatizando sua importância para desempenho e escalonamento nos nós mais avançados.

De 2025 em diante, espera-se que o segmento de litografia de borda irregular cresça a uma taxa de crescimento anual composta (CAGR) superior a 20% até 2030, superando o crescimento do mercado de litografia mais amplo. Essa aceleração é impulsionada pela crescente demanda por computação de alto desempenho, aceleradores de IA e aplicações 5G, todas as quais requerem arquiteturas de dispositivos mais densas e precisas. À medida que grandes fabricantes de chips, como a Samsung Electronics e a Micron Technology, expandem a produção de DRAM, NAND e chips lógicos em nós avançados, espera-se que a demanda por equipamentos e soluções de processo de litografia de borda irregular aumente.

- Até 2027, espera-se que a adoção pela indústria se estenda a um conjunto mais amplo de fundições e IDMs, particularmente na Ásia e na América do Norte, à medida que as estruturas de custo melhorarem e a maturidade do processo aumentar.

- Até 2030, a litografia de borda irregular pode representar até 15% de todas as vendas de ferramentas de litografia avançada, de acordo com projeções de fornecedores de equipamentos líderes.

A perspectiva para a litografia de borda irregular está intimamente ligada a investimentos contínuos em P&D, prontidão da cadeia de suprimentos e colaboração entre fabricantes de equipamentos e produtores de semicondutores. À medida que desafios técnicos forem abordados e eficiências de custo realizadas, a litografia de borda irregular deve desempenhar um papel central na evolução da fabricação avançada de semicondutores ao longo da década.

Fatores de Adoção: Desempenho, Eficiência e Miniaturização

A adoção da litografia de semicondutores de borda irregular está sendo impulsionada por vários fatores convergentes, notavelmente pela demanda incessante por maior desempenho, eficiência energética melhorada e maior miniaturização na fabricação de chips. À medida que a indústria de semicondutores se aproxima dos limites físicos da fotolitografia tradicional, particularmente em nós abaixo de 2 nm, a necessidade de técnicas de padronização inovadoras se tornou urgente. A litografia de borda irregular, que introduz irregularidades controladas em escala nanométrica, está emergindo como uma solução promissora para esses desafios, permitindo características de dispositivos aprimoradas enquanto mantém ou até reduz o consumo de energia.

Um dos principais impulsionadores é a busca por ganhos de desempenho por meio de um controle mais preciso da geometria do canal em transistores. Aproveitando a litografia de borda irregular, os fabricantes podem ajustar as bordas dos transistores, otimizando a mobilidade dos elétrons e reduzindo a variabilidade no comportamento do dispositivo. ASML Holding, um dos principais fornecedores de equipamentos de litografia, destacou a necessidade de tais métodos de padronização avançada para complementar a litografia de ultravioleta extremo (EUV) à medida que a indústria avança em direção a 1,4 nm e além. A abordagem de borda irregular pode proporcionar o aprimoramento da resolução necessário para esses nós ultra-finos, apoiando o desenvolvimento de dispositivos semicondutores mais rápidos e confiáveis.

A eficiência energética é outro impulsionador crítico que fundamenta a adoção da litografia de borda irregular. À medida que os data centers e dispositivos móveis enfrentam crescentes restrições de energia, os fabricantes de chips estão buscando métodos para minimizar correntes de vazamento e otimizar o controle de portões. A capacidade de projetar a rugosidade da borda em escala atômica, como demonstrado por colaborações de pesquisa envolvendo a Intel Corporation e outras grandes fundições, mostrou potencial para reduzir o vazamento em estado desligado e melhorar a transição subthreshold—ambas métricas-chave para eletrônicos de baixo consumo.

A miniaturização continua sendo o cerne da inovação em semicondutores, com dispositivos avançados de lógica e memória exigindo tamanhos de características cada vez menores. O Roadmap Internacional para Dispositivos e Sistemas (IRDS) projeta escalonamento contínuo até o final da década, mas destaca a precisão do posicionamento da borda como um fator limitante. A litografia de borda irregular aborda isso, permitindo uma padronização mais precisa e reproduzível em dimensões atômicas, apoiando a fabricação de Heterojunction FETs (GAA) e outras arquiteturas de próxima geração (IEEE IRDS).

Olhando para 2025 e os anos seguintes, espera-se que líderes da indústria, como TSMC e Samsung Electronics, acelerem as linhas de produção piloto incorporando a litografia de borda irregular, especialmente para chips de computação de alto desempenho e aceleradores de IA. Esses esforços destacam uma tendência mais ampla: à medida que a corrida por semicondutores menores, mais rápidos e mais eficientes se intensifica, a litografia de borda irregular está prestes a se tornar um facilitador essencial da próxima onda de tecnologia de chips.

Desafios Técnicos e Limitações em 2025

A litografia de semicondutores de borda irregular, que se refere a técnicas de padronização que produzem bordas de linha com maior rugosidade ou perfis não ideais, enfrenta desafios técnicos significativos à medida que a indústria entra em 2025. O impulso incessante em direção a nós de processo sub-3 nm e o escalonamento em dispositivos avançados de lógica e memória exacerba o impacto da rugosidade da borda da linha (LER) e da rugosidade da largura da linha (LWR) no desempenho e rendimento do dispositivo.

Um dos principais obstáculos técnicos decorre das limitações dos sistemas atuais de litografia de ultravioleta extremo (EUV). Embora o EUV tenha possibilitado a continuação do escalonamento, efeitos estocásticos—variações aleatórias na absorção de fótons e na química de resistência—levam a um aumento da rugosidade da borda em dimensões ultrafinas. Isso pode resultar em variabilidade nas tensões de limiar de transistor, correntes de vazamento e na confiabilidade geral do circuito. Fabricantes líderes como TSMC e Intel Corporation relataram que à medida que os tamanhos de característica diminuem, o controle da rugosidade da borda está se tornando um gargalo crítico para alcançar um escalonamento adicional e um desempenho satisfatório do dispositivo.

Os fotoresistores usados na litografia EUV permanecem uma fonte-chave de bordas irregulares. Os resistores quimicamente amplificados atuais lutam para equilibrar resolução, sensibilidade e LER/LWR. Esforços para desenvolver novas químicas de resistência e resistores à base de óxido metálico mostraram promessa em ambientes laboratoriais, mas os desafios permanecem na transferência desses materiais para a produção em massa com a uniformidade e controle de processo necessários. De acordo com ASM International, os avanços em materiais de resistência são cruciais, mas a indústria enfrenta uma adoção lenta devido à complexidade de integração e à necessidade de novos controles de processo.

A precisão de sobreposição e erros de posicionamento de padrão também contribuem para efeitos de borda irregular. À medida que os processos de múltiplas padronizações e alinhamento automático se tornam mais complexos, erros cumulativos podem amplificar a rugosidade nas bordas das características, impactando a uniformidade da dimensão crítica (CD). ASML Holding tem trabalhado para melhorar a estabilidade do sistema e a metrologia para as ferramentas EUV de próxima geração, mas mesmo melhorias marginais são desafiadas pela física fundamental nessas escalas.

Olhando para os próximos anos, a perspectiva é mista. A indústria está investindo pesadamente em soluções de metrologia avançadas, como inspeção de feixe eletrônico de alta resolução e medição de CD em linha, para caracterizar melhor e mitigar os defeitos de borda irregular. No entanto, a menos que breakthroughs em engenharia de materiais, formulação de resistores ou controle de processos estocásticos sejam alcançados, a litografia de borda irregular continuará sendo um fator limitante para rendimento e desempenho do dispositivo nos nós mais avançados. Esforços colaborativos entre fabricantes, fabricantes de ferramentas e fornecedores de materiais serão essenciais para superar essas limitações técnicas e permitir progresso adicional no escalonamento de semicondutores.

Cenário Competitivo: Comparando Abordagens Tradicionais vs. de Borda Irregular

O cenário competitivo para a litografia de semicondutores em 2025 está testemunhando uma mudança notável à medida que as técnicas de litografia de borda irregular ganham força ao lado de abordagens tradicionais, como fotolitografia óptica e litografia de ultravioleta extremo (EUV). A fotolitografia tradicional, há muito dominada por processos de ultravioleta profundo (DUV), ainda é a espinha dorsal para a produção em grande volume devido à sua maturidade, escalabilidade e cadeias de suprimento estabelecidas. Players líderes como ASML e TSMC continuam a empurrar os limites da tecnologia EUV, permitindo a produção em massa de nós de 3nm e se aproximando de 2nm. Os sistemas EUV oferecem precisão, mas vêm com custos de capital imensos, requisitos de infraestrutura complexos e retornos decrescentes à medida que os tamanhos de características diminuem ainda mais.

Em contraste, a litografia de semicondutores de borda irregular—às vezes referida como “padronização de borda irregular” ou “mitigação de erro de posicionamento da borda”—surgem como um complemento ou alternativa promissora. Essa abordagem introduz intencionalmente rugosidade controlada das bordas ou irregularidades na máscara ou etapa de padronização do wafer, aproveitando algoritmos avançados e controles de processo para melhorar a fidelidade do padrão ou desempenho elétrico em dimensões nanométricas. Empresas como Synopsys e KLA Corporation estão desenvolvendo novas ferramentas de design para fabricação e metrologia para caracterizar e explorar os efeitos de borda irregular para otimização de dispositivos.

Em 2025, a principal vantagem competitiva da litografia de borda irregular reside em sua capacidade de mitigar erros de posicionamento de borda e rugosidade da borda da linha, duas fontes principais de perda de rendimento e variabilidade à medida que as dimensões críticas se aproximam de 2nm. Isso é especialmente relevante para dispositivos avançados de lógica e memória, onde a variabilidade em escala atômica pode impactar a confiabilidade do dispositivo. Dados preliminares de linhas piloto em fundições como TSMC e Intel indicam que a integração da padronização de borda irregular em combinação com EUV ou DUV pode reduzir o erro de posicionamento em até 30% em comparação com paradigmas de borda lisa tradicionais, levando a melhorias mensuráveis no rendimento e desempenho do dispositivo.

- Abordagens tradicionais (DUV/EUV): Alta produtividade; ecossistema estabelecido; caro e complexo em nós sub-3nm; aumentando desafios de rugosidade da borda e variabilidade (ASML).

- Estratégias de borda irregular: Menor investimento de capital incremental; maior rendimento em escala atômica; compatível com metrologia avançada e fluxos de design computacional; adoção ainda limitada a fábricas pioneiras e arquiteturas de dispositivos específicas (KLA Corporation).

Olhando adiante, a interação competitiva entre a litografia tradicional e a de borda irregular provavelmente se intensificará à medida que o escalonamento dos dispositivos empurrar os limites das técnicas atuais. Espera-se que a adoção de métodos de borda irregular se amplie, especialmente à medida que os fornecedores de ferramentas de EDA e inspeção refinarem suas soluções. No entanto, a ampla adoção pela indústria dependerá de uma validação adicional da confiabilidade e da relação custo-benefício em ambientes de fabricação em alto volume.

Aplicações Emergentes em IA, IoT e Centros de Dados

A litografia de semicondutores de borda irregular, que aproveita a rugosidade intencional da borda e a padronização não uniforme, está ganhando rapidamente impulso à medida que a indústria de semicondutores busca abordagens inéditas para escalonamento de dispositivos e otimização de desempenho. As geometrias únicas possibilitadas pelas técnicas de borda irregular começaram a encontrar aplicações diversas, especialmente em domínios que exigem integração de alta densidade, eficiência energética e robustez da integridade do sinal—exigências-chave em toda a inteligência artificial (IA), Internet das Coisas (IoT) e infraestruturas de centros de dados.

Em 2025, grandes fabricantes de semicondutores estão explorando ativamente a litografia de borda irregular para aceleradores de IA. Esses aceleradores, como GPUs e TPUs, requerem transistores densamente empacotados para maximizar o paralelismo e a capacidade de processamento. Empresas como a Intel e a NVIDIA relataram pesquisas em técnicas de padronização avançada para ultrapassar os limites da densidade lógica e eficiência energética, onde metodologias de borda irregular podem reduzir a capacitância parasita e permitir layouts irregulares e específicos para aplicações. Esses avanços são vitais para cargas de trabalho de IA, que demandam não apenas desempenho bruto, mas também eficiência energética devido ao crescimento exponencial em dados de treinamento e tamanhos de modelos.

Dentro do setor de IoT, a proliferação de dispositivos de borda exige chips ultra compactos e de baixo consumo. A litografia de borda irregular permite formatos de dispositivos irregulares que se alinham com a heterogeneidade das necessidades dos pontos finais de IoT. A TSMC e a Samsung Electronics demonstraram chips protótipos utilizando esquemas de litografia avançada para computação em borda, sugerindo que técnicas de borda irregular poderiam desempenhar um papel significativo nos futuros designs de chips de IoT. A capacidade de otimizar tanto para espaço quanto para função é particularmente benéfica à medida que as implantações de IoT escalam para dezenas de bilhões de dispositivos.

Centros de dados, enfrentando crescentes pressões por eficiência e rendimento, também devem se beneficiar da litografia de borda irregular. Processadores modernos de servidores e módulos de memória, desenvolvidos por empresas como Micron Technology e AMD, estão incorporando geometrias mais apertadas e estratégias de layout inovadoras para minimizar a latência e maximizar a largura de banda por watt. A integração da padronização de borda irregular pode facilitar roteamentos e isolamento mais eficientes, melhorando a fidelidade do sinal e o gerenciamento térmico, que são críticos para ambientes de computação de alto desempenho.

Olhando para o futuro, os próximos anos estão prontos para uma maior integração da litografia de borda irregular em produtos comerciais de IA, IoT e centros de dados. À medida que os líderes do ecossistema continuam a refinar os controles de processo e as cadeias de ferramentas de design, a versatilidade e as vantagens da padronização irregular provavelmente se tornarão comuns, apoiando as exigências cada vez mais especializadas e desafiadoras das aplicações de semicondutores de próxima geração.

Regulamentações, Normas e Diretrizes da Indústria

O rápido avanço da litografia de semicondutores de borda irregular, uma técnica que aproveita a rugosidade controlada da borda para melhorar o desempenho do dispositivo em nós sub-5nm, está atraindo crescente atenção de órgãos reguladores e organizações de padrões em 2025. À medida que os principais fabricantes de chips integram abordagens de borda irregular para estender a Lei de Moore, normas harmonizadas e estruturas regulatórias claras estão se tornando fatores críticos para adoção ampla e interoperabilidade global.

Em 2025, a organização SEMI continua a desempenhar um papel central na reunião de partes interessadas da indústria para refinar padrões de controle de processos de litografia, precisão de posicionamento de borda e metrologia. O Roteiro Internacional de Tecnologia para Semicondutores (ITRS) da SEMI destacou especificamente a necessidade de novas métricas e diretrizes para rugosidade da borda litográfica e variabilidade, que agora são centrais para os processos de litografia de borda irregular. Os padrões atualizados da SEMI, como SEMI P47 para qualificação de fotomáscaras e SEMI M52 para uniformidade da dimensão crítica, estão sendo reexaminados para incorporar parâmetros relevantes para metodologias de borda irregular.

A Associação de Indústrias de Eletrônicos e Tecnologia da Informação do Japão (JEITA) e a Associação Alemã de Máquinas e Equipamentos (VDMA) também lançaram grupos de trabalho em 2025 para tratar de formatos de troca de dados e rastreabilidade de processos específicos para técnicas de borda irregular. Esses esforços visam facilitar a colaboração transfronteiriça e a integridade da cadeia de suprimentos, respondendo à crescente globalização da fabricação de semicondutores.

No front regulatório, o Instituto Nacional de Padrões e Tecnologia (NIST) dos Estados Unidos está desenvolvendo materiais de referência e protocolos para medição de rugosidade da borda em escala nanométrica, com o objetivo de fornecer benchmarks consistentes para a supervisão regulatória e da indústria. O envolvimento do NIST com fabricantes de chips e fornecedores de equipamentos está ajudando a alinhar a ciência de medição com as demandas em evolução da litografia de borda irregular, garantindo que preocupações sobre confiabilidade e segurança dos dispositivos sejam sistematicamente abordadas.

Olhando para o futuro, o consenso da indústria em 2025 aponta para atividades de padronização aceleradas nos próximos anos, com foco na interoperabilidade de plataformas de software e hardware, rastreabilidade de características de borda irregular ao longo da cadeia de suprimentos e conformidade com segurança/ambiental. A colaboração entre organismos de padrões regionais, como CSA Group e ETSI, deve se intensificar, particularmente à medida que a litografia de borda irregular se torne integral à lógica avançada, memória e integração heterogênea. Os anos vindouros devem ver a publicação de diretrizes unificadas e programas de certificação, moldando o cenário regulatório para essa tecnologia transformadora de semicondutores.

Perspectivas Futuras: Roteiro, Potencial Disruptivo e Recomendações Estratégicas

À medida que a indústria de semicondutores se aproxima do marco de 2025, a litografia de borda irregular está pronta para se tornar um ponto focal tanto para melhorias de processo incrementais quanto para mudanças disruptivas potenciais. Essa técnica, que introduz intencionalmente irregularidades geométricas controladas nas bordas dos dispositivos, busca mitigar as limitações litográficas em nós avançados, particularmente à medida que o escalonamento abaixo de 3nm empurra os limites da fotolitografia tradicional e dos sistemas EUV (Ultravioleta Extremo).

Em 2025, espera-se que os principais fabricantes de semicondutores avaliem a litografia de borda irregular como parte de seus roteiros de integração de processos para dispositivos de lógica e memória. Empresas como a Intel Corporation e a Taiwan Semiconductor Manufacturing Company (TSMC) sinalizaram pesquisas contínuas em padronização complementar, múltiplas padronizações e correção de erro de posicionamento de borda, todas relacionadas ao potencial da aplicação de estratégias de borda irregular. Fabricantes de ferramentas como ASML Holding também estão desenvolvendo soluções de metrologia e exposição que poderiam apoiar a complexidade de processo aumentada associada à padronização não retangular.

Artigos técnicos recentes e atas de conferências de organizações como SEMI e o consórcio de Tecnologia de Fabricação de Semicondutores (SEMATECH) indicam que a litografia de borda irregular oferece várias vantagens possíveis. Essas incluem melhor controle da rugosidade da borda, redução de defeitos aleatórios e sistemáticos e maior tolerância à variabilidade estocástica inerente às exposições EUV. Dados de testes iniciais de linhas piloto sugerem que recursos de sub-2nm fabricados com máscaras de borda irregular podem alcançar até 15% melhor uniformidade de dimensão crítica em comparação com abordagens convencionais.

Olhando para o futuro, o potencial disruptivo da litografia de borda irregular reside em sua capacidade de habilitar o contínuo escalonamento de dispositivos sem recorrer a sistemas de EUV ou alta-NA de próxima geração, que são proibitivamente caros. Se os desafios de fabricabilidade—como complexidade de máscaras, inspeção e precisão de sobreposição—puderem ser abordados, as técnicas de borda irregular poderão atrasar ou complementar a necessidade de conjuntos de ferramentas inteiramente novos, oferecendo caminhos custo-efetivos para fundições e fabricantes de dispositivos integrados.

Estratégicamente, recomenda-se que os stakeholders da indústria:

- Envolvam-se em colaborações entre fornecedores com provedores de equipamentos como Carl Zeiss AG para soluções de fabricação de máscaras e inspeção.

- Participem de consórcios e organismos de padrões da indústria como a SEMI para acelerar o desenvolvimento de melhores práticas e padrões de processo.

- Inverstam em produção piloto e metrologia em linha para validar os benefícios de borda irregular para linhas de produtos específicas.

Em resumo, até 2025 e na segunda metade da década, espera-se que a litografia de semicondutores de borda irregular passe de exploração conceitual para implantação direcionada, moldando a abordagem da indústria para a fabricação de nós sub-3nm e potencialmente redefinindo o cenário litográfico.

Fontes & Referências

- ASML

- Infineon Technologies AG

- Canon Inc.

- TOK

- JSR Corporation

- imec

- KLA Corporation

- Tokyo Electron

- Micron Technology

- IEEE IRDS

- ASM International

- Synopsys

- NVIDIA

- Associação de Indústrias de Eletrônicos e Tecnologia da Informação do Japão (JEITA)

- Associação Alemã de Máquinas e Equipamentos (VDMA)

- Instituto Nacional de Padrões e Tecnologia (NIST)

- CSA Group

- Carl Zeiss AG