目次

- エグゼクティブサマリー: 2025年、ジャギーエッジリソグラフィーの交差点にて

- 技術概要: ジャギーエッジリソグラフィーの仕組み

- 主要プレーヤーとイノベーター: 主要企業と業界アライアンス

- 市場規模と2030年までの成長予測

- 採用推進要因: 性能、効率、ミニチュア化

- 2025年における技術的課題と制限

- 競争環境: 従来型アプローチとジャギーエッジアプローチの比較

- AI、IoT、データセンターにおける新たな応用

- 規制、基準、および業界ガイドライン

- 将来の展望: ロードマップ、破壊的潜在能力、および戦略的推奨

- 参考文献

エグゼクティブサマリー: 2025年、ジャギーエッジリソグラフィーの交差点にて

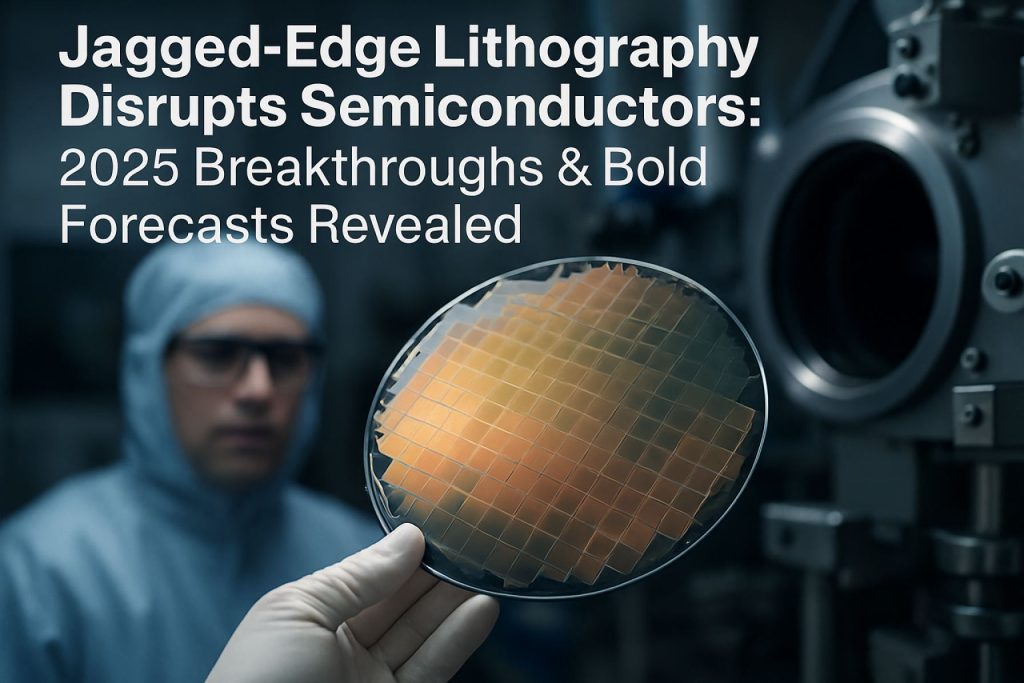

2025年、ジャギーエッジ半導体リソグラフィーは重要な交差点に立っており、次世代デバイス製造に固有の約束と課題の両方を反映しています。業界は、2nm未満のノードと高度なパッケージングに向けた絶え間ない追求を続けており、従来のフォトリソグラフィーの限界が浮き彫りになっています。これにより、主要な製造業者は、ラインエッジ粗さ(LER)および変動性の問題を克服するために、ジャギーエッジや「ジャギーライン」パターン技術を探求しています。ASMLやインテル社といった主要なプレーヤーは、極紫外線(EUV)リソグラフィーと補完的なパターンプロセスの洗練に対して公にコミットしており、ジャギーエッジ戦略は、必要な解像度と歩留まりを達成するためにますます重要になっています。

最近のマスク技術とレジスト材料の進展により、エッジの定義をより正確に制御できるようになりました。TSMCとサムスン電子は、1.4nmおよび2nmノードをターゲットにしたパイロット生産において、デバイスの均一性が向上し、エッジの粗さが低減されたと報告しています。これらの開発は、新しいレジスト化学物質と高NA(数値開口)EUVスキャナーへの継続的な投資に直接結びついています。ASMLは、論理とメモリアプリケーションの両方におけるジャギーエッジパターン制御を最適化するためにデバイスメーカーと積極的に協力しています。

これらの技術的進歩にもかかわらず、近い将来におけるジャギーエッジリソグラフィーの見通しは微妙です。コストと複雑性の懸念が広がり、グローバルファウンドリーズとインフィニオンテクノロジーズは、高ボリュームでの採用のためのプロセスウィンドウの狭まりと欠陥管理を持続的な障害として特定しています。業界のコンソーシアム、例えばSEMIは、ジャギーエッジプロセスメトロロジーの標準化と既存のEUVおよびDUV(深紫外線)インフラとの統合を加速するための共同研究を促進しています。

今後数年は、マスクの忠実度、レジストの感度、プロセス制御ソフトウェアにおける反復的な改善によって定義されるでしょう。AI、高性能コンピューティング、車両アプリケーション向けのチップ需要が急増する中、ジャギーエッジパターンを一貫してスケールで再現する能力は、マーケットリーダーシップにおける決定的な要因となります。2027年までに、業界はジャギーエッジリソグラフィーが特殊な技術から主流の先進ノードの実現の手段に移行することを期待していますが、技術的および経済的障壁が機器サプライヤー、ファウンドリー、および材料の革新者の間の継続的なコラボレーションを通じて十分に対処される必要があります。

技術概要: ジャギーエッジリソグラフィーの仕組み

ジャギーエッジ半導体リソグラフィーは、先端パターニングプロセスにおける戦略的進展を示しており、ナノスケールでエッジ粗さの意図的な設計と制御に焦点を当てています。従来のリソグラフィーは、トランジスタや相互接続部のためにできるだけ滑らかな特性エッジを生成することを重視していますが、ジャギーエッジリソグラフィーは、パターンのエッジに沿って制御された不規則性を活用して、新しいデバイスアーキテクチャを可能にし、デバイス性能を向上させる可能性があります。

2025年におけるジャギーエッジリソグラフィーのコアワークフローは、深紫外線(DUV)およびますます極紫外線(EUV)フォトリソグラフィーツールに依存しています。ASMLやキヤノン株式会社などの主要な業界サプライヤーは、10nm未満のパターン形成に必要な先進的な露光システムを提供しています。しかし、異なる点は、マスクとレジストの設計、ならびに意図的に露光パターンを変調して滑らかなラインエッジではなく、ジャギーのようなラインエッジを生成するための高度なプロセス制御アルゴリズムにあります。これは、望ましいエッジ粗さとウエハー表面における光子および電子の相互作用の確率的性質を考慮して、最適なマスク形状を計算する計算リソグラフィー技術を通じて達成されます。

材料の革新も重要であり、TOK(東京オカ工業)やJSR株式会社は、意図的なエッジ特性を信頼性の高い方法で再現し、EUV露光の高エネルギー条件下でパターン忠実度を維持できる新しいフォトレジスト化学を開発しています。プロセスフローには、ブロックコポリマー材料が事前にパターン化されたジャギーテンプレートによって誘導される方向性自己組織化(DSA)技術が組み込まれる可能性があり、この方法は、imecなどの共同コンソーシアムによって探求されています。

インラインメトロロジーと検査において、KLA Corporationのような半導体機器のリーダーは、原子スケールのラインエッジ粗さ(LER)およびライン幅粗さ(LWR)を定量化するために測定システムを進化させており、ジャギー性が目標仕様内にあることを保証しています。プロセス制御は、製造中にエッジ属性をリアルタイムで予測、監視、調整するための高度な計算モデルと機械学習アルゴリズムによってさらに支援されます。

今後、ジャギーエッジリソグラフィーは次世代の論理およびメモリデバイスの製造において採用が増加すると期待されており、パイロット生産がEUVダブルパターニングやマスク最適化を使用する特定のファウンドリーで進行中です。エッジ粗さを操作する能力は、デバイスエンジニアリングにおいて新たなフロンティアを開き、量子トンネリング制御や変動性エンジニアリングが先進的な研究や製造組織によって積極的に探求されています。

主要プレーヤーとイノベーター: 主要企業と業界アライアンス

ジャギーエッジ半導体リソグラフィーの開発と商業化は、制御されたエッジ粗さを利用して従来の方法の解像度限界を克服するために設計された技術であり、主要な半導体機器製造業者と協力的な業界アライアンス間で競争の焦点となっています。2025年までに、いくつかの主要なプレーヤーがこの技術を積極的に推進しており、次世代ノードの製造に統合し、論理デバイスとメモリデバイスの両方におけるその可能性を探求しています。

ASMLは、極紫外線(EUV)リソグラフィーシステムの主要な供給者として、ジャギーエッジ技術の進化において中心的な役割を果たしています。最近のEUVプラットフォームのアップデートには、エッジ配置誤差(EPE)補正モジュールと高度なパターン制御が組み込まれており、2nm以下のノードにおけるジャギーエッジパターニングに必要な厳密なオーバーレイと粗さ管理を可能にしています。2024年、ASMLは主要なファウンドリーと提携し、ジャギーエッジ機能の製造実現性を検証し、選定された顧客サイトでのパイロットランが開始されましたASML。

東京エレクトロン(TEL)は、ジャギーエッジマスクパターンを原子精度でシリコンに変換するために必要なエッチングおよび堆積装置においてリーダーとして登場しました。TELの2024年に導入された最新のドライエッチングプラットフォームは、エッジ粗さのリアルタイム監視と適応制御を提供し、SRAMや高性能DRAMの製造でジャギーエッジリソグラフィーの大規模な採用を促進します東京エレクトロン。

アプライド マテリアルズは、プロセス制御とメトロロジーにおける専門知識を活かしてジャギーエッジリソグラフィーを支援しています。同社の最新の検査ツールは機械学習アルゴリズムを搭載し、エッジ粗さ測定でサブナノメートルの解像度を提供し、このパターン形成アプローチが大規模な製造に入る際に不可欠なフィードバックループを可能にしますアプライド マテリアルズ。

imecやSEMIのような業界アライアンスも重要であり、競争前の研究と企業間の共同作業のための中立的な場となっています。imecの2024年の研究プログラムでは、1.4nmノードでジャギーエッジリソグラフィーを使用した最初の集積回路が実証されており、ツールメーカーおよび材料サプライヤーと密接に連携しています。一方、SEMIはエッジ粗さメトリクスの標準化とリソグラフィーとメトロロジーシステム間の相互運用性を促進しています。

今後数年を見据え、これらの企業とアライアンスは、特に業界が従来のパターニングのスケーリング限界に直面する中でジャギーエッジリソグラフィーの採用を加速させると期待されています。パイロットラインが初期生産に移行し、より多くのファブが高度な制御システムを統合することで、ジャギーエッジ技術は2nm未満のテクノロジーノードとその先の実現において中心的な役割を果たす準備が整っています。

市場規模と2030年までの成長予測

ジャギーエッジ半導体リソグラフィーは、先端ノードにおける従来のフォトリソグラフィーの限界に対処するために設計された最先端のパターニング技術であり、2030年までの大幅な成長が期待されています。この技術は、半導体業界が3nm未満のプロセスノードに向けて進む中で特に重要であり、ラインエッジ粗さ、パターン忠実度、デバイスの変動性が重要な要素となります。2025年において、ジャギーエッジリソグラフィーの採用は、次世代の論理およびメモリデバイスに投資する先端ファウンドリーや統合デバイスメーカー(IDM)の間で主に見られます。

業界のリーダーからの現在の推定によれば、グローバルな半導体リソグラフィー機器市場は2025年に約250億ドルと評価され、ジャギーエッジリソグラフィー工具は小さいながらも急速に拡大しているシェアを占めるとされています。ASMLやキヤノン株式会社などのパイオニア企業は、ジャギーエッジパターニングをサポートできるリソグラフィープラットフォームの開発と販売に積極的に取り組んでおり、しばしば高度なEUV(極紫外線)および複数パターニング技術を活用してこれらの機能を可能にしています。TSMCやインテル社は、このような革新を自社の先端製造計画に統合しており、最も先進的なノードにおける性能とスケーリングの重要性を強調しています。

2025年以降、ジャギーエッジリソグラフィーセグメントは2030年までに20%を超える年平均成長率(CAGR)で成長することが予想されており、より広範なリソグラフィー市場の成長を上回ると見込まれています。この加速は、高性能コンピューティング、AIアクセラレーター、5Gアプリケーションへの需要の高まりに起因しており、これらはすべて、より密で正確なデバイスアーキテクチャを必要とします。サムスン電子やマイクロンテクノロジーなどの主要なチップメーカーが、先端ノードでDRAM、NAND、論理チップの生産を拡大する中で、ジャギーエッジリソグラフィー機器およびプロセスソリューションの需要が急増することが期待されます。

- 2027年までに、業界の採用は、特にコスト構造が改善され、プロセスの成熟度が向上する中で、アジアおよび北米のより広範なファウンドリーやIDMに拡大する見込みです。

- 2030年までに、ジャギーエッジリソグラフィーは、先進的なリソグラフィーツール販売の最大15%を占める可能性があると、主要な機器サプライヤーからの予測によるとされています。

ジャギーエッジリソグラフィーの展望は、継続的なR&D投資、サプライチェーンの準備状況、機器メーカーと半導体プロデューサー間のコラボレーションに密接に関連しています。技術的課題が対処されてコスト効率が実現されるにつれ、ジャギーエッジリソグラフィーは、今後10年間の先端半導体製造の進化において中心的な役割を果たすことが期待されています。

採用推進要因: 性能、効率、ミニチュア化

ジャギーエッジ半導体リソグラフィーの採用は、主により高い性能、改善されたエネルギー効率、さらにチップ製造のミニチュア化を求める複数の要因によって推進されています。半導体業界が特に2nm未満のノードにおける従来のフォトリソグラフィーの物理的限界に迫る中、新しいパターニング技術の必要性が急を要する課題となっています。ナノスケールで意図的な不規則性を導入するジャギーエッジリソグラフィーは、これらの課題に対する有望な解決策として浮上しており、性能を向上させながらエネルギー消費を維持または減少させることを可能にします。

主な推進要因の一つは、トランジスタ内のチャネル幾何学の精密な制御を通じて性能向上を追求することです。ジャギーエッジリソグラフィーを活用することで、製造者はトランジスタのエッジを微調整し、電子移動度を最適化し、デバイスの挙動における変動性を低減できます。ASMLホールディングは、業界が1.4nm以上に向かう中で、極紫外線(EUV)リソグラフィーを補完するためにそのような高度なパターニング手法の必要性を強調しています。ジャギーエッジアプローチは、これらの非常に微細なノードに求められる解像度の向上を提供し、より高速で信頼性の高い半導体デバイスの開発を支援することができます。

エネルギー効率も、ジャギーエッジリソグラフィーの採用を支える重要な要因です。データセンターやモバイルデバイスが増大する電力制約に直面する中、チップメーカーはリーク電流を最小化し、ゲート制御を最適化する方法を模索しています。インテル社と他の主要なファウンドリーが関与する研究協力によって示されたように、原子スケールでエッジ粗さをエンジニアリングする能力は、オフステートリークを低減し、サブスレッショルドスイングを改善する可能性を示しています。これらはすべて、低電力エレクトロニクスにおける重要な指標です。

ミニチュア化は半導体のイノベーションの中心にあり、高度な論理デバイスやメモリデバイスはますます小さな特徴サイズを要求しています。国際デバイスおよびシステムのロードマップ(IRDS)は、10年の終わりまでスケーリングの継続を予測していますが、エッジ配置精度を制限因子として強調しています。ジャギーエッジリソグラフィーは、原子寸法でより正確かつ再現可能なパターニングを可能にすることにより、ゲートオールアラウンド(GAA)FETや他の次世代アーキテクチャの製造をサポートします(IEEE IRDS)。

2025年以降、TSMCやサムスン電子などの業界リーダーが、特に高性能コンピューティングやAIアクセラレーター向けチップのジャギーエッジリソグラフィーを組み込んだパイロット生産ラインを加速すると予想されています。これらの努力は、より小型で迅速かつ効率的な半導体を求める競争の中で、ジャギーエッジリソグラフィーが次の波のチップ技術の必須な実現手段となることを示しています。

2025年における技術的課題と制限

ジャギーエッジ半導体リソグラフィーは、ラインエッジの粗さや非理想的なプロファイルを持つパターンを生成する技術であり、業界が2025年に入る中で重大な技術的課題に直面しています。サブ3nmプロセスノードと高度な論理およびメモリデバイスのスケーリングに向けた絶え間ない追求は、デバイスの性能や歩留まりへのラインエッジ粗さ(LER)やライン幅粗さ(LWR)の影響を悪化させています。

主な技術的障害の一つは、現在の極紫外線(EUV)リソグラフィーシステムの限界から生じています。EUVはスケーリングを可能にしましたが、確率的効果—つまり光子の吸収やレジスト化学のランダムな変動—は、これらの超微細な寸法でエッジ粗さを増加させる要因となります。これにより、トランジスタのしきい値電圧やリーク電流、回路全体の信頼性に変動が生じることがあります。TSMCやインテル社といった主要な製造業者は、特徴サイズが縮小するにつれて、エッジ粗さの制御がさらなるスケーリングと満足のいくデバイス性能を実現するための重要なボトルネックになっていると報告しています。

EUVリソグラフィーに使用されるフォトレジストもジャギーエッジの主要な原因です。現在の化学的に増幅されたレジストは、解像度、感度、およびLER/LWRのバランスを取るのが難しいとされています。新しいレジスト化学と金属酸化物ベースのレジストの開発は、実験室での設定で期待が持てる結果を示していますが、これらの材料を必要な均一性とプロセス制御を備えた大量生産に移行するには課題が残ります。ASM Internationalによれば、レジスト材料の進展は重要ですが、新しいプロセス制御の必要性や統合の複雑性のために、業界では採用が遅れているとされています。

オーバーレイ精度やパターン配置誤差も、ジャギーエッジ効果に寄与しています。マルチパターニングやセルフアラインドプロセスが複雑になるにつれて、累積誤差が特徴のエッジでの粗さを増幅させ、重要な寸法(CD)の均一性に影響を与える可能性があります。ASMLホールディングは、次世代EUVツールのためのシステムの安定性とメトロロジーの改善に取り組んでいますが、これらのスケールでの基本的な物理学によってさえも困難が伴います。

今後数年を見据えた展望は混合しています。業界は、ジャギーエッジ欠陥を特定し、軽減するために高解像度電子ビーム検査やインラインCD測定などの高度なメトロロジーソリューションに大きな投資を行っています。ただし、材料工学、レジスト配合、あるいは確率的プロセス制御においてブレークスルーが実現されない限り、ジャギーエッジリソグラフィーは、最も先進的なノードでの歩留まりやデバイス性能の制約要因として残るでしょう。製造業者、ツールメーカー、および材料サプライヤー間の協力が、こうした技術的限界を克服し、半導体のスケーリングのさらなる進展を可能にするために重要です。

競争環境: 従来型アプローチとジャギーエッジアプローチの比較

2025年における半導体リソグラフィーの競争環境は、ジャギーエッジリソグラフィー技術が従来の光学リソグラフィーおよび極紫外線(EUV)リソグラフィーと共に進展している中で著しい変化を遂げています。従来のフォトリソグラフィーは、長年にわたり深紫外線(DUV)プロセスによって支配されてきたため、高ボリューム生産のバックボーンとして成熟性、スケーラビリティ、確立されたサプライチェーンを提供しています。ASMLやTSMCのような主要プレーヤーは、3nmの量産を可能にするEUV技術の限界を押し広げ続けていますが、EUVシステムは高額な資本コスト、複雑なインフラ要件、および特徴サイズのさらなる縮小に伴う減少するリターンを伴います。

対照的に、ジャギーエッジ半導体リソグラフィー—時には「ジャギーエッジパターニング」または「エッジ配置誤差の緩和」と呼ばれる—は、思慮深い補完性または代替手段として浮上しています。このアプローチは、マスクまたはウエハパターンングステップにおいて意図的に制御されたエッジ粗さや不規則性を導入し、ナノスケールでパターン忠実度や電気性能を向上させるために高度なアルゴリズムやプロセス制御を活用しています。SynopsysやKLA Corporationのような企業は、デバイス最適化のためにジャギーエッジ効果を特定し、利用する新しい製造設計およびメトロロジーツールを開発しています。

2025年において、ジャギーエッジリソグラフィーの主な競争優位性は、2nmに近づく重要寸法での歩留まり損失や変動性の二大要因であるエッジ配置誤差とラインエッジ粗さを軽減できる能力にあります。これは、原子スケールの変動性がデバイスの信頼性に影響を与える可能性がある高度な論理およびメモリデバイスに特に関連しています。TSMCやインテルのようなファウンドリーのパイロットラインからの初期データは、ジャギーエッジパターニングをEUVやDUVと組み合わせることで、従来のスムーズエッジパラダイムと比較してエッジ配置誤差を最大30%削減できることを示唆しており、デバイスの歩留まりや性能において測定可能な改善につながっています。

- 従来型アプローチ(DUV/EUV): 高スループット; 確立されたエコシステム; 3nm未満のノードでは高コストで複雑; エッジ粗さと変動性の課題が増加(ASML)。

- ジャギーエッジ戦略: 低い追加資本投資; 原子スケールでの歩留まりの向上; 高度なメトロロジーおよび計算設計フローとの互換性; 採用は依然として先駆的なファブや特定のデバイスアーキテクチャに限定されています(KLA Corporation)。

今後を見据えると、従来型リソグラフィーとジャギーエッジリソグラフィーの間の競争は、デバイススケーリングが現在の技術の限界を押し広げる中で、顕著化する可能性があります。ジャギーエッジ手法の採用は、特にEDAおよび検査ツールのプロバイダーがそのソリューションを洗練させるにつれて、広がることが期待されています。しかし、広範な業界全体の採用は、高量産製造環境における信頼性やコスト対効果のさらなる検証に依存します。

AI、IoT、データセンターにおける新たな応用

ジャギーエッジ半導体リソグラフィーは、意図的なエッジ粗さや不均一なパターンを活用し、デバイスのスケーリングや性能最適化のために急速に注目を集めています。ジャギーエッジ技術によって可能になるユニークなジオメトリは、高密度統合、電力効率、ロバストな信号整合性を要求されるドメイン—人工知能(AI)、モノのインターネット(IoT)、データセンターインフラにおいて多岐にわたって応用が始まっています。

2025年、主要な半導体メーカーはAIアクセラレーターのためにジャギーエッジリソグラフィーを積極的に探求しています。これらのアクセラレーター(たとえばGPUやTPU)は、並列処理と計算スループットを最大化するために高密度にパッケージ化されたトランジスタを必要とします。インテルやNVIDIAなどの企業は、論理密度とエネルギー効率を高めるために先進的なパターニング技術の研究に取り組んでおり、ジャギーエッジ手法は寄生キャパシタンスを低減し、アプリケーション特有の不規則なレイアウトを可能にします。これらの進展は、AIワークロードにおいてますます重要であり、トレーニングデータやモデルサイズの指数的成長から生じるエネルギー効率と生の性能が求められています。

IoTセクターにおいては、エッジデバイスの普及が超コンパクトで低消費電力のチップを必要としています。ジャギーエッジリソグラフィーが不規則なデバイスのフットプリントを許容することは、IoTエンドポイントの要求の異質性に合致しています。TSMCやサムスン電子は、エッジコンピューティングのための先進的なリソグラフィー方式を利用したプロトタイプチップを示しており、ジャギーエッジ技術が将来のIoTチップデザインで重要な役割を果たす可能性を示唆しています。スペースと機能を最適化する能力は、IoTの展開が数十億台のデバイスにスケールする中で特に有用です。

データセンターは、効率性とスループットの圧力が高まる中で、ジャギーエッジリソグラフィーから利益を得る可能性があります。マイクロンテクノロジーやAMDのような企業が開発した現代のサーバー用プロセッサやメモリモジュールは、レイテンシを最小化し、ワットあたりの帯域幅を最大化するために厳密なジオメトリおよび新たなレイアウト戦略を取り入れています。ジャギーエッジパターニングを統合することで、ルーティングと絶縁をより効率的にし、信号整合性や熱管理を向上させることができ、高性能コンピューティング環境において重要です。

今後数年は、商業用AI、IoT、データセンター製品におけるジャギーエッジリソグラフィーのさらなる統合が予想されます。エコシステムのリーダーがプロセス制御と設計ツールチェーンを洗練させ続ける中で、不規則なパターニングの多様性と利点が主流になる可能性が高く、次世代半導体アプリケーションの要求に応えることが期待されます。

規制、基準、および業界ガイドライン

ジャギーエッジ半導体リソグラフィーの急速な進展は、2025年に規制当局や標準化機関からの注目を集めています。この技術は、5nm未満のノードで改善されたデバイス性能のために制御されたエッジ粗さを活用しています。主要なチップメーカーは、ムーアの法則を延長するためにジャギーエッジアプローチを統合している中、調和の取れた基準と明確な規制フレームワークが広範な採用とグローバルな相互運用性のための重要な要素として浮上しています。

2025年においても、SEMI組織は、リソグラフィープロセス制御、エッジ配置精度、メトロロジーの基準を洗練させるために、業界の関係者を招集する中心的な役割を果たしています。SEMIの国際半導体技術ロードマップ(ITRS)は、リソグラフィーにおけるエッジ粗さや変動性のための新しいメトリクスとガイドラインの必要性を特に強調しており、これらは現在のジャギーエッジリソグラフィーのプロセスの中心に位置しています。SEMIの更新された基準、たとえばフォトマスク資格のためのSEMI P47や重要寸法の均一性のためのSEMI M52は、ジャギーエッジ手法に関連するパラメータを組み込むよう見直されています。

日本電子情報技術産業協会(JEITA)やドイツのVerband Deutscher Maschinen- und Anlagenbau(VDMA)は、2025年にジャギーエッジ技術に特化したデータ交換フォーマットやプロセストレースビリティに関する作業部会を立ち上げています。これらの努力は、半導体製造の国際化に対応し、国を越えた協力やサプライチェーンの整合性を促進することを目指しています。

規制の面では、米国の国立標準技術研究所(NIST)がナノスケールのエッジ粗さ測定のための基準材料やプロトコルを開発しており、業界および規制監視のための一貫したベンチマークを提供することを目指しています。NISTのチップメーカーや機器サプライヤーとの関与は、測定科学がジャギーエッジリソグラフィーの進化する要求に合わせて調整されるのを助け、デバイスの信頼性とセキュリティに関する懸念が体系的に対処されることを確実にします。

今後を見据えると、2025年には業界の合意が、今後数年間にわたり、ソフトウェアおよびハードウェアプラットフォームの相互運用性、ジャギーエッジ機能のサプライチェーン全体でのトレーサビリティ、安全性/環境適合を重視した標準化活動の加速を指し示しています。CSAグループやETSIのような地域標準機関間の協力は、ジャギーエッジリソグラフィーが先進論理、メモリ、および異種集積の統合に不可欠となる中で強化されることが期待されています。今後数年のうちに統一されたガイドラインや認証プログラムが発表され、この変革的な半導体技術の規制の風景を形成することになるでしょう。

将来の展望: ロードマップ、破壊的潜在能力、および戦略的推奨

半導体業界が2025年のマイルストーンに近づく中、ジャギーエッジリソグラフィーはプロセス改善の焦点として、また潜在的な破壊的シフトのポイントとなることが期待されています。この技術は、デバイスのエッジに制御された幾何学的不規則性を意図的に導入することによって、特に3nm未満のスケーリングがのリソグラフィー限界を緩和しようとしています。

2025年には、主要な半導体メーカーが論理およびメモリデバイスのプロセス統合ロードマップの一部としてジャギーエッジリソグラフィーを評価することが期待されています。インテル社や台湾積体電路製造(TSMC)などは、補完的パターニング、多重パターニング、およびエッジ配置誤差補正における継続的な研究を示しており、これらはジャギーエッジ戦略の潜在的な応用に関連しています。ASMLホールディングのようなツールメーカーは、非直線的なパターニングに関連する処理の複雑さをサポートするメトロロジーおよび露光ソリューションを開発しています。

SEMIや半導体製造技術(SEMATECH)コンソーシアムのような組織からの最近の技術論文や会議の議事録は、ジャギーエッジリソグラフィーがいくつかの可能な利点を提供することを示しています。これには、ラインエッジ粗さ制御の改善、ランダムおよび系統的欠陥の削減、EUV露光に固有の確率的変動に対する耐性の向上が含まれます。パイロットラインからの初期テストデータは、ジャギーエッジマスクを使用して製造されたサブ2nm機能が、従来のアプローチに比べて最大15%優れたクリティカルディメンションの均一性を達成できることを示唆しています。

将来的には、ジャギーエッジリソグラフィーの破壊的潜在能力は、次世代の高コストなEUVや高NAシステムに頼ることなく、継続的なデバイスのスケーリングを実現する能力にあります。マスクの複雑さ、検査、オーバーレイ精度などの製造可能性の課題が解決できれば、ジャギーエッジ手法は新たなツールセットの必要性を遅らせたり補完したりすることができ、ファウンドリーや統合デバイスメーカーにとって費用対効果の高い道を提供する可能性があります。

戦略的に、業界の関係者には以下が推奨されます。

- リソグラフィー機器を提供する業者とマスク製作や検査ソリューションでクロスサプライヤー連携を行う。

- 業界のベストプラクティスやプロセス標準の開発を加速するために、SEMIのような業界コンソーシアムや基準団体に参加する。

- 特定の製品ラインのジャギーエッジの利点を検証するために、パイロット生産とインラインメトロロジーに投資する。

要するに、2025年から10年代の後半にかけて、ジャギーエッジ半導体リソグラフィーは概念的な探求からターゲットを絞った展開へと移行し、サブ3nmノードの製造へのアプローチを形成し、リソグラフィーの風景を根本的に再定義する可能性が期待されています。

参考文献

- ASML

- インフィニオンテクノロジーズ

- キヤノン株式会社

- TOK

- JSR株式会社

- imec

- KLA Corporation

- 東京エレクトロン

- マイクロンテクノロジー

- IEEE IRDS

- ASM International

- Synopsys

- NVIDIA

- 日本電子情報技術産業協会 (JEITA)

- ドイツ機械工業連盟(VDMA)

- 米国国立標準技術研究所(NIST)

- CSAグループ

- カール・ツァイスAG