Tabla de Contenidos

- Resumen Ejecutivo: 2025 en el Cruce de la Litografía de Borde Irregular

- Visión General de Tecnología: Cómo Funciona la Litografía de Borde Irregular

- Jugadores Clave e Innovadores: Empresas Líderes y Alianzas Industriales

- Tamaño del Mercado y Previsiones de Crecimiento Hasta 2030

- Motores de Adopción: Desempeño, Eficiencia y Miniaturización

- Desafíos Técnicos y Limitaciones en 2025

- Paisaje Competitivo: Comparando Enfoques Tradicionales y de Borde Irregular

- Aplicaciones Emergentes en IA, IoT y Centros de Datos

- Normas Regulatorias y Directrices de la Industria

- Perspectivas Futuras: Hoja de Ruta, Potencial Disruptivo y Recomendaciones Estratégicas

- Fuentes y Referencias

Resumen Ejecutivo: 2025 en el Cruce de la Litografía de Borde Irregular

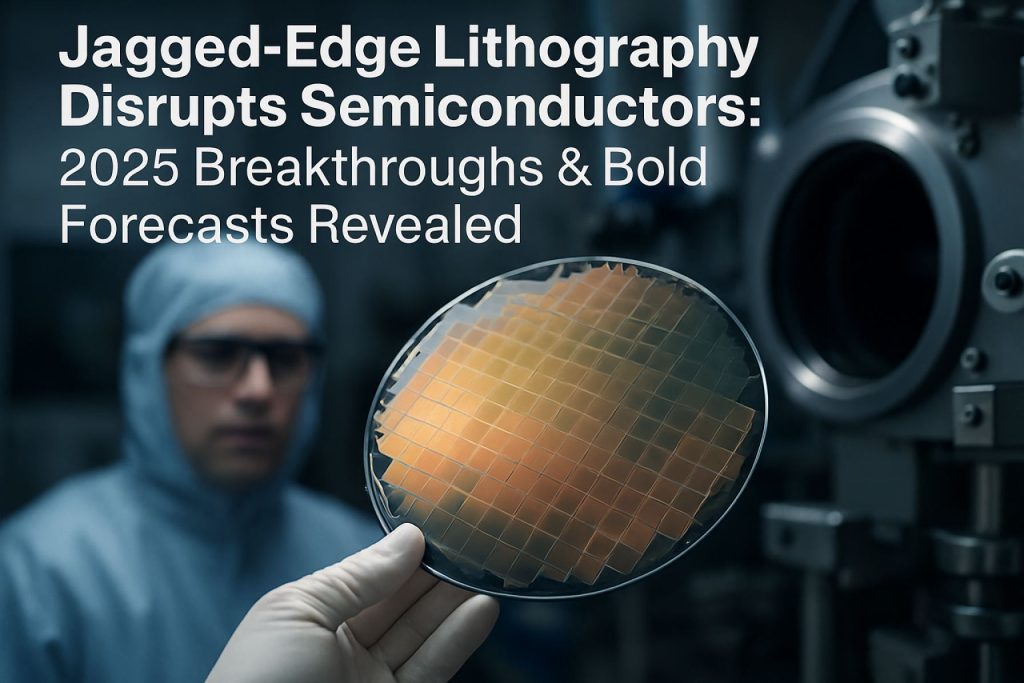

En 2025, la litografía de semiconductores de borde irregular se encuentra en un cruce crucial, reflejando tanto la promesa como los desafíos inherentes a la fabricación de dispositivos de próxima generación. El impulso implacable de la industria hacia nodos inferiores a 2 nm y empaque avanzado ha expuesto los límites de la fotolitografía convencional, lo que ha llevado a los principales fabricantes a explorar técnicas de patrón de borde irregular o «línea dentada» para superar los problemas de rugosidad de los bordes de línea (LER) y variabilidad. Jugadores importantes como ASML e Intel Corporation se han comprometido públicamente a perfeccionar la litografía de ultravioleta extremo (EUV) y procesos de patrón complementarios, con estrategias de borde irregular volviéndose cada vez más críticas para lograr la resolución y el rendimiento requeridos.

Los avances recientes en tecnología de máscaras y materiales de resistencia han permitido un control más preciso sobre la definición del borde, con TSMC y Samsung Electronics informando sobre una mayor uniformidad de dispositivos y una reducción de la rugosidad de los bordes en producciones piloto que apuntan a los nodos de 1.4 nm y 2 nm. Estos desarrollos están directamente relacionados con las inversiones continuas en novel chemistries de resistencia y escáneres EUV de alta NA (apertura numérica), como se destacó en las sesiones informativas tecnológicas de 2024 de ASML, que está colaborando activamente con los fabricantes de dispositivos para optimizar el control de patrón de borde irregular para aplicaciones de lógica y memoria.

A pesar de estos avances técnicos, las perspectivas para la litografía de borde irregular a corto plazo son matizadas. Las preocupaciones sobre costos y complejidad son prominentes, con GlobalFoundries e Infineon Technologies AG identificando la reducción de ventanas de proceso y la gestión de defectos como obstáculos continúos para la adopción a gran escala. Consorcios de la industria, incluyendo SEMI, están fomentando investigaciones colaborativas para acelerar la estandarización en torno a la metrología de procesos de borde irregular e integración con la infraestructura existente de EUV y DUV (ultravioleta profundo).

Mirando hacia el futuro, los próximos años estarán definidos por mejoras iterativas en la fidelidad de máscara, la sensibilidad de resistencias y el software de control de procesos. Con la demanda de chips aumentando para IA, computación de alto rendimiento y aplicaciones automotrices, la capacidad de replicar consistentemente patrones de borde irregular a gran escala será un factor decisivo en el liderazgo del mercado. Para 2027, la industria anticipa que la litografía de borde irregular transitará de ser una técnica especializada a un habilitador convencional para nodos avanzados, siempre que se aborden suficientemente las barreras técnicas y económicas a través de la colaboración continua entre proveedores de equipos, fundiciones e innovadores de materiales.

Visión General de Tecnología: Cómo Funciona la Litografía de Borde Irregular

La litografía de semiconductores de borde irregular representa una evolución estratégica en los procesos avanzados de patrón, enfocándose en el diseño y control intencionado de la rugosidad del borde a escala nanométrica. A diferencia de la litografía convencional, que enfatiza la producción de bordes de características lo más suaves posible para transistores e interconexiones, la litografía de borde irregular aprovecha irregularidades controladas a lo largo del borde de los patrones para permitir arquitecturas de dispositivos novedosas y potencialmente mejorar el rendimiento del dispositivo.

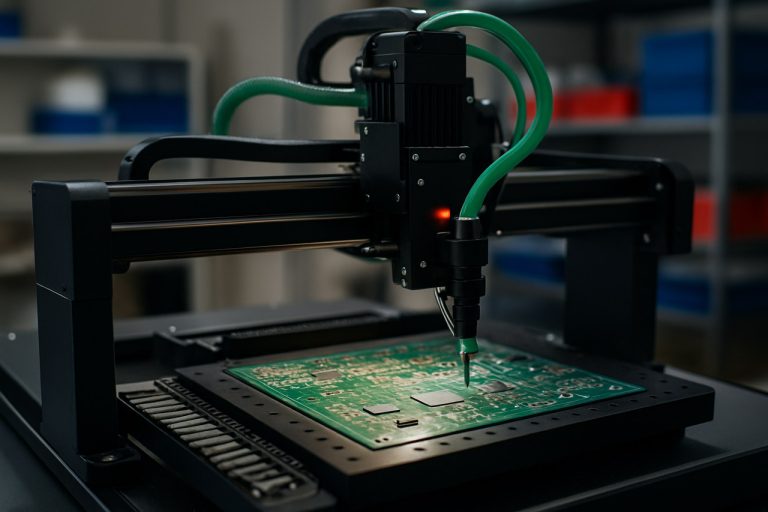

El flujo de trabajo central de la litografía de borde irregular en 2025 aún depende de herramientas de fotolitografía de ultravioleta profundo (DUV) y cada vez más de ultravioleta extremo (EUV), con proveedores clave de la industria como ASML y Canon Inc. proporcionando los sistemas de exposición avanzados necesarios para el patrón sub-10 nm. Sin embargo, la diferencia radica en el diseño de máscaras y resistencias, así como en algoritmos sofisticados de control de procesos que modulan intencionadamente el patrón de exposición para producir bordes de línea irregulares, en lugar de perfectamente rectos. Esto se logra a través de técnicas de litografía computacional que calculan la forma óptima de la máscara, teniendo en cuenta la rugosidad del borde deseada y la naturaleza estocástica de las interacciones de fotones y electrones en la superficie del wafer.

Las innovaciones en materiales también son críticas, con empresas como TOK (Tokyo Ohka Kogyo) y JSR Corporation desarrollando nuevas chemistries de fotoresistencia que pueden reproducir de manera confiable características de borde intencionadas y mantener la fidelidad del patrón bajo las condiciones de alta energía de la exposición a EUV. El flujo del proceso puede incorporar técnicas de autoensamble dirigido (DSA), en las que materiales de copolímero de bloques son guiados por plantillas irregulares prepatronadas, amplificando aún más las irregularidades del borde de manera controlada, un método explorado por consorcios colaborativos como imec.

Para la metrología e inspección en línea, líderes en equipos de semiconductores como KLA Corporation han avanzado en sus sistemas de medición para cuantificar la rugosidad del borde de línea (LER) y la rugosidad del ancho de línea (LWR) a escalas atómicas, asegurando que la irregularidad se mantenga dentro de las especificaciones objetivo. El control de procesos se apoya aún más en modelos computacionales avanzados y algoritmos de aprendizaje automático para predecir, monitorear y ajustar los atributos del borde en tiempo real durante la fabricación.

Mirando hacia adelante, se espera que la litografía de borde irregular vea una creciente adopción en la fabricación de dispositivos de lógica y memoria de próxima generación, con producciones piloto ya en marcha en fundiciones selectas utilizando doble patrón EUV y optimización de máscaras. La capacidad de manipular la rugosidad del borde abre nuevas fronteras en la ingeniería de dispositivos, incluyendo control de túneles cuánticos y ingeniería de variabilidad, que están siendo explorados activamente por organizaciones líderes en investigación y fabricación.

Jugadores Clave e Innovadores: Empresas Líderes y Alianzas Industriales

El desarrollo y la comercialización de la litografía de semiconductores de borde irregular, una técnica diseñada para superar los límites de resolución de los métodos tradicionales aprovechando la rugosidad controlada del borde, se ha convertido en un foco competitivo entre los principales fabricantes de equipos de semiconductores y alianzas industriales colaborativas. A partir de 2025, varios actores clave están avanzando activamente en esta tecnología, integrándola en la fabricación de nodos de próxima generación y explorando su potencial tanto para dispositivos de lógica como de memoria.

ASML, el proveedor dominante de sistemas de litografía de ultravioleta extremo (EUV), sigue siendo central en la evolución de las técnicas de borde irregular. Las actualizaciones recientes de la plataforma EUV de la compañía han incorporado módulos de corrección de errores de colocación de bordes (EPE) y controles avanzados de patrón, permitiendo una gestión más precisa de la superposición y la rugosidad requeridas para el patrón de borde irregular en nodos inferiores a 2 nm. En 2024, ASML se asoció con principales fundiciones para validar la viabilidad de producción de características de borde irregular, comenzando producciones piloto en sitios de clientes seleccionados ASML.

Tokyo Electron (TEL) se ha convertido en un líder en equipos de grabado y deposición críticos para traducir patrones de máscara de borde irregular en silicio con precisión atómica. Las últimas plataformas de grabado en seco de TEL, introducidas en 2024, ofrecen monitoreo en tiempo real y control adaptativo de la rugosidad del borde, facilitando la adopción masiva de la litografía de borde irregular para la producción de SRAM y DRAM avanzados Tokyo Electron.

Applied Materials está aprovechando su experiencia en control de procesos y metrología para apoyar la litografía de borde irregular. Las últimas herramientas de inspección de la compañía, que cuentan con algoritmos de aprendizaje automático, ahora proporcionan resolución sub-nanométrica en la medición de la rugosidad del borde, habilitando bucles de retroalimentación esenciales para la mejora del rendimiento a medida que este enfoque de patrón entra en la fabricación a gran escala Applied Materials.

Las alianzas industriales como imec y SEMI también son fundamentales, actuando como terrenos neutrales para la investigación precompetitiva y la colaboración entre empresas. Los programas de investigación de imec en 2024 demostraron los primeros circuitos integrados utilizando litografía de borde irregular en el nodo de 1.4 nm, trabajando estrechamente con fabricantes de herramientas y proveedores de materiales. SEMI, por otro lado, está facilitando esfuerzos de estandarización en torno a métricas de rugosidad del borde y la interoperabilidad entre sistemas de litografía y metrología.

Mirando hacia adelante en los próximos años, se espera que estas empresas y alianzas aceleren la adopción de la litografía de borde irregular, particularmente a medida que la industria enfrente los límites de escalado de los patrones convencionales. Con líneas piloto avanzando hacia la producción inicial y más fábricas integrando sistemas de control avanzados, las técnicas de borde irregular están listas para desempeñar un papel central en habilitar nodos tecnológicos inferiores a 2 nm y más allá.

Tamaño del Mercado y Previsiones de Crecimiento Hasta 2030

La litografía de semiconductores de borde irregular, una tecnología de patrón de vanguardia diseñada para abordar las limitaciones de la fotolitografía convencional en nodos avanzados, está lista para un crecimiento sustancial hasta 2030. Esta técnica es particularmente relevante a medida que la industria de semiconductores avanza hacia nodos de proceso inferiores a 3 nm, donde la rugosidad de los bordes de línea, la fidelidad del patrón y la variabilidad del dispositivo se convierten en factores críticos. En 2025, la adopción de la litografía de borde irregular se observa principalmente entre fundiciones de vanguardia y fabricantes de dispositivos integrados (IDMs) que invierten en dispositivos de lógica y memoria de próxima generación.

Las estimaciones actuales de líderes de la industria indican que el mercado global de equipos de litografía de semiconductores está valorado en aproximadamente $25 mil millones en 2025, con herramientas de litografía de borde irregular representando una pequeña pero rápidamente creciente participación. Pioneros como ASML y Canon Inc. están desarrollando y comercializando activamente plataformas de litografía capaces de soportar patrones de borde irregular, aprovechando a menudo técnicas avanzadas de EUV (Ultravioleta Extremo) y múltiples patrones para habilitar estas características. TSMC e Intel Corporation han integrado tales innovaciones en sus hojas de ruta de fabricación avanzada, enfatizando su importancia para el rendimiento y la escalabilidad en los nodos más avanzados.

Desde 2025 en adelante, se pronostica que el segmento de litografía de borde irregular crecerá a una tasa de crecimiento anual compuesta (CAGR) que superará el 20% hasta 2030, superando el crecimiento del mercado de litografía en general. Esta aceleración es impulsada por la creciente demanda de computación de alto rendimiento, aceleradores de IA y aplicaciones de 5G, todas las cuales requieren arquitecturas de dispositivos más densas y precisas. A medida que los principales fabricantes de chips como Samsung Electronics y Micron Technology amplían la producción de DRAM, NAND y chips de lógica en nodos avanzados, se espera que la demanda de equipos de litografía de borde irregular y soluciones de proceso aumente.

- Para 2027, se espera que la adopción de la industria se extienda a un conjunto más amplio de fundiciones y IDMs, particularmente en Asia y América del Norte, a medida que las estructuras de costos mejoren y la madurez del proceso aumente.

- Para 2030, la litografía de borde irregular podría representar hasta el 15% de todas las ventas de herramientas de litografía avanzadas, según proyecciones de los principales proveedores de equipos.

Las perspectivas para la litografía de borde irregular están estrechamente vinculadas a las inversiones continuas en I+D, la preparación de la cadena de suministro y la colaboración entre fabricantes de equipos y productores de semiconductores. A medida que se abordan los desafíos técnicos y se realiza la eficiencia de costos, se espera que la litografía de borde irregular desempeñe un papel central en la evolución de la fabricación avanzada de semiconductores a lo largo de la década.

Motores de Adopción: Desempeño, Eficiencia y Miniaturización

La adopción de la litografía de semiconductores de borde irregular está siendo impulsada por varios factores convergentes, notablemente la demanda incesante de mayor rendimiento, mejor eficiencia energética y mayor miniaturización en la fabricación de chips. A medida que la industria de semiconductores se acerca a los límites físicos de la fotolitografía tradicional, particularmente en nodos por debajo de 2 nm, la necesidad de técnicas de patrón innovadoras se ha vuelto urgente. La litografía de borde irregular, que introduce irregularidades controladas a escala nanométrica, está surgiendo como una solución prometedora para estos desafíos, permitiendo características mejoradas del dispositivo mientras mantiene o incluso reduce el consumo de energía.

Uno de los principales motores es la búsqueda de ganancias de rendimiento mediante un control más preciso de la geometría del canal en transistores. Al aprovechar la litografía de borde irregular, los fabricantes pueden ajustar los bordes de los transistores, optimizando la movilidad de electrones y reduciendo la variabilidad en el comportamiento del dispositivo. ASML Holding, un proveedor líder de equipos de litografía, ha destacado la necesidad de tales métodos de patrón avanzados para complementar la litografía de ultravioleta extremo (EUV) a medida que la industria avanza hacia 1.4 nm y más allá. El enfoque de borde irregular puede proporcionar la mejora de resolución necesaria para estos nodos ultrafinos, apoyando el desarrollo de dispositivos semiconductores más rápidos y confiables.

La eficiencia energética es otro motor crítico que subyace a la adopción de la litografía de borde irregular. A medida que los centros de datos y los dispositivos móviles enfrentan restricciones de energía crecientes, los fabricantes de chips están buscando métodos para minimizar las corrientes de fuga y optimizar el control de compuertas. La capacidad de diseñar la rugosidad de los bordes a escala atómica, como lo han demostrado las colaboraciones de investigación que involucran a Intel Corporation y otras grandes fundiciones, ha mostrado potencial para reducir la fuga en estado apagado y mejorar la oscilación sub umbral, ambos métricas clave para la electrónica de bajo consumo.

La miniaturización sigue siendo el núcleo de la innovación semiconductor, con dispositivos de lógica y memoria avanzados que requieren tamaños de características cada vez más pequeños. La Hoja de Ruta Internacional para Dispositivos y Sistemas (IRDS) proyecta una continua escala hacia el final de la década, pero destaca la precisión de colocación del borde como un factor limitante. La litografía de borde irregular aborda esto al permitir un patrón más preciso y reproducible a dimensiones atómicas, apoyando la fabricación de transistores de compuerta envolvente (GAA) y otras arquitecturas de próxima generación (IEEE IRDS).

Mirando hacia 2025 y los años siguientes, se espera que líderes de la industria como TSMC y Samsung Electronics aceleren las líneas de producción piloto que incorporan la litografía de borde irregular, especialmente para chips de computación de alto rendimiento y aceleradores de IA. Estos esfuerzos subrayan una tendencia más amplia: a medida que la carrera por semiconductores más pequeños, más rápidos y más eficientes se intensifica, la litografía de borde irregular está lista para convertirse en un habilitador esencial de la próxima ola de tecnología de chips.

Desafíos Técnicos y Limitaciones en 2025

La litografía de semiconductores de borde irregular, que se refiere a técnicas de patrón que producen bordes de línea con mayor rugosidad o perfiles no ideales, enfrenta desafíos técnicos significativos a medida que la industria ingresa a 2025. El impulso incesante hacia nodos de proceso inferiores a 3 nm y el escalado en dispositivos de lógica y memoria avanzados agravan el impacto de la rugosidad de los bordes de línea (LER) y la rugosidad del ancho de línea (LWR) en el rendimiento y la rentabilidad del dispositivo.

Uno de los principales obstáculos técnicos proviene de las limitaciones de los sistemas actuales de litografía de ultravioleta extremo (EUV). Si bien EUV ha permitido el escalado continuo, los efectos estocásticos—variaciones aleatorias en la absorción de fotones y la química de la resistencia—conllevan un aumento de la rugosidad de los bordes en estas dimensiones ultrafinas. Esto puede resultar en variabilidad en los voltajes de umbral de transistores, corrientes de fuga y confiabilidad general del circuito. Fabricantes líderes como TSMC e Intel Corporation han informado que a medida que los tamaños de características disminuyen, el control de la rugosidad de los bordes se está convirtiendo en un cuello de botella crítico para lograr un escalado adicional y un rendimiento satisfactorio del dispositivo.

Las fotoresistencias utilizadas para la litografía EUV siguen siendo una fuente clave de bordes irregulares. Las resistencias químicamente amplificadas actuales luchan por equilibrar la resolución, la sensibilidad y LER/LWR. Los esfuerzos para desarrollar nuevas chemistries de resistencia y resistencias basadas en óxido metálico han mostrado promesas en entornos de laboratorio, pero persisten desafíos para transferir estos materiales a la producción en masa con la uniformidad y el control de procesos necesarios. Según ASM International, los avances en materiales de resistencia son cruciales, pero la adopción de la industria es lenta debido a la complejidad de integración y la necesidad de nuevos controles de proceso.

La precisión de la superposición y los errores de colocación de patrones también contribuyen a los efectos de borde irregular. A medida que los procesos de múltiples patrones y auto-alineación se vuelven más complejos, los errores acumulativos pueden amplificar la rugosidad en los bordes de las características, afectando la uniformidad de dimensión crítica (CD). ASML Holding ha estado trabajando para mejorar la estabilidad del sistema y la metrología de las herramientas EUV de próxima generación, pero incluso mejoras marginales se ven desafiadas por la física fundamental a estas escalas.

Mirando hacia los próximos años, las perspectivas son mixtas. La industria está invirtiendo fuertemente en soluciones de metrología avanzadas, como inspección de electrones de alta resolución y mediciones de CD en línea, para caracterizar mejor y mitigar defectos de borde irregular. Sin embargo, a menos que se logren avances en ingeniería de materiales, formulación de resistencias o control de procesos estocásticos, la litografía de borde irregular seguirá siendo un factor limitante para la rentabilidad y el rendimiento de los dispositivos en los nodos más avanzados. Los esfuerzos colaborativos entre fabricantes, fabricantes de herramientas y proveedores de materiales serán esenciales para superar estas limitaciones técnicas y permitir un progreso adicional en el escalado de semiconductores.

Paisaje Competitivo: Comparando Enfoques Tradicionales y de Borde Irregular

El paisaje competitivo para la litografía de semiconductores en 2025 está presenciando un cambio notable a medida que las técnicas de litografía de borde irregular ganan tracción junto con enfoques tradicionales como la litografía óptica y la litografía de ultravioleta extremo (EUV). La fotolitografía tradicional, dominada durante mucho tiempo por procesos de ultravioleta profundo (DUV), sigue siendo la columna vertebral de la producción de alto volumen debido a su madurez, escalabilidad y cadenas de suministro establecidas. Jugadores líderes como ASML y TSMC continúan empujando los límites de la tecnología EUV, permitiendo la producción en masa de nodos de 3 nm y acercándose a 2 nm. Los sistemas EUV ofrecen precisión, pero vienen con costos de capital inmensos, requisitos de infraestructura compleja y retornos decrecientes a medida que los tamaños de características se reducen aún más.

En contraste, la litografía de semiconductores de borde irregular— a veces denominada «patrón de borde irregular» o «mitigación de errores de colocación de bordes» — surge como un complemento o alternativa prometedora. Este enfoque introduce intencionadamente una rugosidad controlada en el borde o irregularidades en el paso de patronización de la máscara o del wafer, aprovechando algoritmos avanzados y controles de proceso para mejorar la fidelidad del patrón o el rendimiento eléctrico en dimensiones nanométricas. Empresas como Synopsys y KLA Corporation están desarrollando nuevas herramientas de diseño para fabricación y metrología para caracterizar y explotar los efectos de borde irregular para la optimización de dispositivos.

En 2025, la principal ventaja competitiva de la litografía de borde irregular radica en su capacidad para mitigar errores de colocación de bordes y rugosidad de borde de línea, dos fuentes importantes de pérdida de rendimiento y variabilidad a medida que las dimensiones críticas se acercan a 2 nm. Esto es especialmente relevante para dispositivos de lógica y memoria avanzados, donde la variabilidad a escala atómica puede impactar la confiabilidad del dispositivo. Datos preliminares de líneas piloto en fundiciones como TSMC e Intel indican que integrar el patrón de borde irregular en combinación con EUV o DUV puede reducir el error de colocación de borde hasta un 30% en comparación con paradigmas de bordes lisos tradicionales, lo que conduce a mejoras medibles en el rendimiento y la rentabilidad del dispositivo.

- Enfoques tradicionales (DUV/EUV): Alta capacidad de producción; ecosistema establecido; costosos y complejos en nodos sub-3 nm; desafíos crecientes de rugosidad y variabilidad (ASML).

- Estrategias de borde irregular: Menor inversión de capital incremental; mayor rendimiento a escala atómica; compatibles con metrología avanzada y flujos de diseño computacionales; adopción aún limitada a fábricas pioneras y arquitecturas de dispositivos específicas (KLA Corporation).

Mirando hacia adelante, la interacción competitiva entre la litografía tradicional y la de borde irregular probablemente se intensificará a medida que el escalado de dispositivos empuje los límites de las técnicas actuales. Se espera que la adopción de métodos de borde irregular se amplíe, especialmente a medida que los proveedores de herramientas de EDA e inspección refinan sus soluciones. Sin embargo, la adopción generalizada por parte de la industria dependerá de una validación adicional de fiabilidad y análisis costo-beneficio en entornos de fabricación a gran escala.

Aplicaciones Emergentes en IA, IoT y Centros de Datos

La litografía de semiconductores de borde irregular, que aprovecha la rugosidad controlada de los bordes y el patrón no uniforme, está ganando rápidamente impulso a medida que la industria de semiconductores busca enfoques novedosos para el escalado de dispositivos y la optimización del rendimiento. Las geometrías únicas que permiten las técnicas de borde irregular han comenzado a encontrar diversas aplicaciones, especialmente en dominios que exigen una integración de alta densidad, eficiencia energética y una robusta integridad de señal—requisitos clave en infraestructuras de inteligencia artificial (IA), Internet de las Cosas (IoT) y centros de datos.

En 2025, los principales fabricantes de semiconductores están explorando activamente la litografía de borde irregular para aceleradores de IA. Estos aceleradores, como los GPU y TPU, requieren transistores densamente empaquetados para maximizar el paralelismo y el rendimiento computacional. Empresas como Intel y NVIDIA han informado sobre investigaciones en técnicas avanzadas de patrón para llevar al límite la densidad lógica y la eficiencia energética, donde las metodologías de borde irregular pueden reducir la capacitancia parasitaria y permitir diseños irregulares específicos para aplicaciones. Estos avances son vitales para cargas de trabajo de IA, que exigen cada vez más no solo rendimiento bruto, sino también eficiencia energética debido al crecimiento exponencial en datos de entrenamiento y tamaños de modelos.

Dentro del sector de IoT, la proliferación de dispositivos en los bordes necesita chips ultra compactos y de bajo consumo. La litografía de borde irregular, que permite huellas de dispositivos irregulares, se alinea con la heterogeneidad de los requisitos de los puntos finales de IoT. TSMC y Samsung Electronics han demostrado chips prototipo que utilizan esquemas de litografía avanzados para computación de borde, sugiriendo que las técnicas de borde irregular podrían desempeñar un papel significativo en los futuros diseños de chips para IoT. La capacidad de optimizar tanto el espacio como la función es particularmente beneficiosa a medida que las implementaciones de IoT escalan a decenas de miles de millones de dispositivos.

Los centros de datos, enfrentando presiones crecientes por eficiencia y rendimiento, también podrían beneficiarse de la litografía de borde irregular. Los procesadores de servidor modernos y los módulos de memoria, desarrollados por empresas como Micron Technology y AMD, están incorporando geometrías más ajustadas y estrategias de diseño novedosas para minimizar la latencia y maximizar el ancho de banda por vatio. La integración de patrones de borde irregular puede facilitar un enrutamiento y aislamiento más eficientes, mejorando la fidelidad de la señal y la gestión térmica, que son críticas para entornos de computación de alto rendimiento.

Mirando hacia adelante, se espera que los próximos años estén destinados a una mayor integración de la litografía de borde irregular en productos comerciales de IA, IoT y centros de datos. A medida que los líderes del ecosistema continúan refinando los controles de proceso y las cadenas de herramientas de diseño, la versatilidad y las ventajas de los patrones irregulares están destinadas a convertirse en algo común, apoyando los requisitos cada vez más especializados y exigentes de las aplicaciones semiconductoras de próxima generación.

Normas Regulatorias y Directrices de la Industria

El rápido avance de la litografía de semiconductores de borde irregular, una técnica que aprovecha la rugosidad de los bordes controlada para mejorar el rendimiento del dispositivo en nodos inferiores a 5 nm, está atrayendo una atención creciente de los organismos reguladores y organizaciones de estándares en 2025. A medida que los principales fabricantes de chips integran enfoques de borde irregular para extender la Ley de Moore, normas armonizadas y marcos regulatorios claros están emergiendo como factores críticos para la adopción generalizada y la interoperabilidad global.

En 2025, la organización SEMI sigue jugando un papel central en la reunión de partes interesadas de la industria para refinar normas para el control de procesos de litografía, precisión de colocación de bordes y metrología. La Hoja de Ruta Internacional de Tecnología para Semiconductores (ITRS) de SEMI ha destacado específicamente la necesidad de nuevas métricas y directrices para la rugosidad y variabilidad del borde litográfico, que son ahora centrales para los procesos de litografía de borde irregular. Las normas actualizadas de SEMI, como SEMI P47 para calificación de fotomáscaras y SEMI M52 para uniformidad de dimensión crítica, están siendo reevaluadas para incorporar parámetros relevantes a las metodologías de borde irregular.

La Asociación de Industrias de Electrónica y Tecnología de la Información de Japón (JEITA) y el Asociación Alemana de Maquinaria e Ingeniería (VDMA) también han lanzado grupos de trabajo en 2025 para abordar formatos de intercambio de datos y trazabilidad de procesos específicos para técnicas de borde irregular. Estos esfuerzos buscan facilitar la colaboración transfronteriza y la integridad de la cadena de suministro, respondiendo a la creciente globalización de la fabricación de semiconductores.

En el frente regulatorio, el Instituto Nacional de Estándares y Tecnología (NIST) en los Estados Unidos está desarrollando materiales de referencia y protocolos para la medición de la rugosidad de los bordes a escala nanométrica, con el objetivo de proporcionar puntos de referencia consistentes para la supervisión industrial y reguladora. La participación de NIST con fabricantes de chips y proveedores de equipos está ayudando a alinear la ciencia de medición con las demandas evolutivas de la litografía de borde irregular, asegurando que se aborden sistemáticamente las preocupaciones sobre la confiabilidad y seguridad del dispositivo.

Mirando hacia adelante, el consenso de la industria en 2025 apunta a actividades de estandarización aceleradas en los próximos años, con un enfoque en la interoperabilidad de plataformas de software y hardware, trazabilidad de las características de borde irregular a lo largo de la cadena de suministro y cumplimiento normativo/ambiental. Se espera que la colaboración entre organismos de estándares regionales, como CSA Group y ETSI, se intensifique, particularmente a medida que la litografía de borde irregular se convierta en parte integral de la lógica avanzada, la memoria y la integración heterogénea. Los próximos años probablemente verán la publicación de directrices unificadas y programas de certificación, dando forma al paisaje regulatorio para esta tecnología transformadora de semiconductores.

Perspectivas Futuras: Hoja de Ruta, Potencial Disruptivo y Recomendaciones Estratégicas

A medida que la industria de semiconductores se acerca al hito de 2025, la litografía de borde irregular está lista para convertirse en un punto focal tanto para la mejora incremental de procesos como para posibles cambios disruptivos. Esta técnica, que introduce intencionadamente irregularidades geométricas controladas en los bordes de los dispositivos, busca mitigar las limitaciones litográficas en nodos avanzados, particularmente a medida que el escalado por debajo de 3 nm empuja los límites de la fotolitografía tradicional y los sistemas EUV (Ultravioleta Extremo).

En 2025, se espera que los principales fabricantes de semiconductores evalúen la litografía de borde irregular como parte de sus hojas de ruta de integración de procesos para dispositivos de lógica y memoria. Empresas como Intel Corporation y Taiwan Semiconductor Manufacturing Company (TSMC) han señalado investigaciones continuas en técnicas de patrones complementarios, múltiples patrones y corrección de errores de colocación de bordes, todas las cuales se relacionan con la aplicación potencial de estrategias de borde irregular. Fabricantes de herramientas como ASML Holding también están desarrollando soluciones de metrología y exposición que podrían apoyar la aumentada complejidad de procesos asociada con la patronización no rectilínea.

Los recientes documentos técnicos y actas de conferencias de organizaciones como SEMI y el consorcio de Tecnología de Fabricación de Semiconductores (SEMATECH) indican que la litografía de borde irregular ofrece varias ventajas posibles. Estas incluyen un mejor control de la rugosidad de los bordes de línea, reducción en defectos aleatorios y sistemáticos, y mayor tolerancia a la variabilidad estocástica inherente a las exposiciones EUV. Los primeros datos de prueba de líneas piloto sugieren que las características de menos de 2 nm fabricadas con máscaras de borde irregular pueden lograr hasta un 15% mejor uniformidad de dimensión crítica en comparación con enfoques convencionales.

Mirando hacia adelante, el potencial disruptivo de la litografía de borde irregular reside en su capacidad para habilitar la continua escalación de dispositivos sin recurrir a sistemas de EUV de próxima generación o de alta NA prohibitivamente costosos. Si se pueden abordar los desafíos de fabricabilidad—como la complejidad de las máscaras, la inspección y la precisión de superposición—las técnicas de borde irregular podrían retrasar o complementar la necesidad de conjuntos de herramientas completamente nuevos, ofreciendo vías rentables para fundiciones y fabricantes de dispositivos integrados.

Estrategicamente, se aconseja a las partes interesadas de la industria:

- Participar en colaboraciones entre proveedores con fabricantes de equipos como Carl Zeiss AG para soluciones de fabricación y inspección de máscaras.

- Participar en consorcios de la industria y organismos de estándares como SEMI para acelerar el desarrollo de mejores prácticas y estándares de proceso.

- Invertir en producción piloto y metrología en línea para validar los beneficios de borde irregular para líneas de productos específicas.

En resumen, para 2025 y en la segunda mitad de la década, se espera que la litografía de semiconductores de borde irregular pase de la exploración conceptual a la implementación dirigida, moldeando el enfoque de la industria hacia la fabricación de nodos inferiores a 3 nm y potencialmente redefiniendo el paisaje litográfico.

Fuentes y Referencias

- ASML

- Infineon Technologies AG

- Canon Inc.

- TOK

- JSR Corporation

- imec

- KLA Corporation

- Tokyo Electron

- Micron Technology

- IEEE IRDS

- ASM International

- Synopsys

- NVIDIA

- Asociación de Industrias de Electrónica y Tecnología de la Información de Japón (JEITA)

- Asociación Alemana de Maquinaria e Ingeniería (VDMA)

- Instituto Nacional de Estándares y Tecnología (NIST)

- CSA Group

- Carl Zeiss AG