Spis treści

- Podsumowanie: 2025 na rozdrożu litografii o postrzępionej krawędzi

- Przegląd technologii: Jak działa litografia o postrzępionej krawędzi

- Kluczowi gracze i innowatorzy: Wiodące firmy i alianse przemysłowe

- Wielkość rynku i prognozy wzrostu do 2030 roku

- Czynniki przyjęcia: Wydajność, efektywność i miniaturyzacja

- Wyzwania techniczne i ograniczenia w 2025 roku

- Krajobraz konkurencji: Porównanie tradycyjnych i postrzępionych podejść

- Nowe zastosowania w AI, IoT i centrach danych

- Standardy regulacyjne i wytyczne branżowe

- Perspektywy na przyszłość: Mapa drogowa, potencjał zakłócający i rekomendacje strategiczne

- Źródła i odniesienia

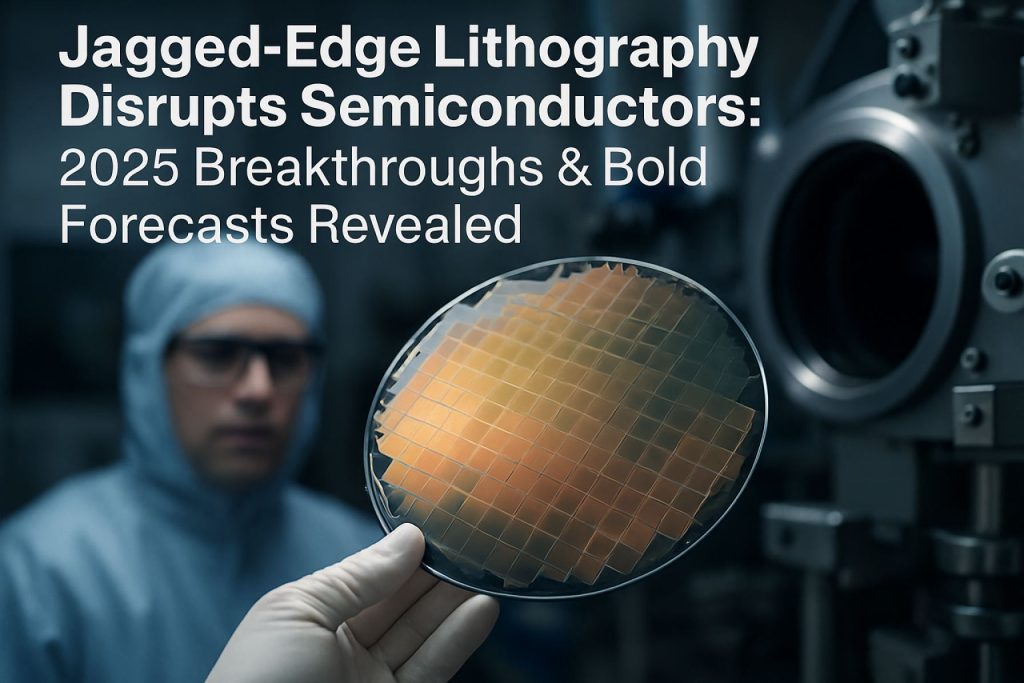

Podsumowanie: 2025 na rozdrożu litografii o postrzępionej krawędzi

W 2025 roku litografia o postrzępionej krawędzi w przemyśle półprzewodnikowym stoi przed kluczowym rozdrożem, odzwierciedlając obietnice i wyzwania związane z produkcją urządzeń nowej generacji. Nieustanny rozwój branży w kierunku węzłów sub-2nm i zaawansowanego pakowania ujawnia ograniczenia konwencjonalnej fotolitografii, zmuszając czołowych producentów do poszukiwania technik wzorcowania z postrzępioną krawędzią, aby pokonać problemy związane z chropowatością krawędzi linii (LER) i zmiennością. Główne podmioty, takie jak ASML oraz Intel Corporation, publicznie zobowiązały się do doskonalenia litografii ekstremalnego ultrafioletu (EUV) oraz komplementarnych procesów wzorcowania, a strategie z postrzępioną krawędzią stają się coraz bardziej kluczowe dla osiągnięcia wymaganej rozdzielczości i wydajności.

Ostatnie osiągnięcia w technologii masek i materiałach rezystywnych umożliwiły dokładniejsze kontrolowanie definiowania krawędzi, przy czym TSMC i Samsung Electronics zgłaszają poprawę jednorodności urządzeń i zmniejszenie chropowatości krawędzi w próbnym produkcie mającym na celu węzły 1.4nm i 2nm. Rozwój ten jest bezpośrednio związany z bieżącymi inwestycjami w nowe chemie rezystów i skanery EUV o wysokiej NA (numerical aperture), co zostało podkreślone w technicznych prezentacjach w 2024 roku przez ASML, które aktywnie współpracuje z producentami urządzeń, aby zoptymalizować kontrolę wzorców o postrzępionych krawędziach dla zastosowań logicznych i pamięci.

Mimo tych postępów technologicznych, perspektywy dla litografii o postrzępionej krawędzi w krótkim okresie pozostają złożone. Obawy dotyczące kosztów i złożoności są widoczne, a GlobalFoundries i Infineon Technologies AG wskazują na zwężanie okien procesowych i zarządzanie defektem jako ciągłe przeszkody w przyjęciu w dużych ilościach. Konsorcja przemysłowe, w tym SEMI, wspierają współpracę w badaniach, aby przyspieszyć standardyzację w zakresie metrologii procesów o postrzępionych krawędziach i integracji z istniejącą infrastrukturą EUV i DUV (głęboki ultrafiolet).

Patrząc w przyszłość, następne kilka lat będą zdefiniowane przez iteracyjne poprawy w doskonałości masek, wrażliwości rezystów i oprogramowania do kontroli procesów. W obliczu gwałtownego wzrostu zapotrzebowania na chipy dla AI, komputerów wysokowydajnych i zastosowań motoryzacyjnych, zdolność do konsekwentnego replikowania wzorców o postrzępionych krawędziach na dużą skalę będzie kluczowym czynnikiem przywództwa na rynku. Do 2027 roku przemysł przewiduje, że litografia o postrzępionej krawędzi przejdzie z techniki specjalistycznej do podstawowego umożliwiacza dla zaawansowanych węzłów, o ile techniczne i ekonomiczne bariery zostaną wystarczająco rozwiązane poprzez dalszą współpracę między dostawcami sprzętu, fabrykami a innowatorami materiałów.

Przegląd technologii: Jak działa litografia o postrzępionej krawędzi

Litografia o postrzępionej krawędzi w półprzewodnikach reprezentuje strategiczną ewolucję w zaawansowanych procesach wzorcowania, koncentrując się na intencjonalnym projektowaniu i kontrolowaniu chropowatości krawędzi na nanoskalę. W przeciwieństwie do konwencjonalnej litografii, która podkreśla produkcję jak najgładszych krawędzi cech dla tranzystorów i połączeń, litografia o postrzępionej krawędzi wykorzystuje kontrolowane nieregularności wzdłuż krawędzi wzorców, aby umożliwić nowe architektury urządzeń i potencjalnie poprawić wydajność urządzenia.

Podstawowy proces litografii o postrzępionej krawędzi w 2025 roku wciąż opiera się na narzędziach fotolitografii głębokiego ultrafioletu (DUV) i coraz częściej również narzędziach EUV, z kluczowymi dostawcami branżowymi, takimi jak ASML i Canon Inc., zapewniającymi zaawansowane systemy ekspozycji konieczne do wzorcowania poniżej 10 nm. Jednak różnicowanie polega na projektowaniu masek i rezystów oraz na skomplikowanych algorytmach kontroli procesów, które intencjonalnie modulują wzór ekspozycji, aby uzyskać postrzępione a nie perfekcyjnie proste krawędzie linii. Osiąga się to poprzez techniki litografii obliczeniowej, które obliczają optymalny kształt maski, biorąc pod uwagę pożądaną chropowatość krawędzi oraz stochastyczny charakter interakcji fotonów i elektronów na powierzchni wafla.

Innowacje materiałowe są również kluczowe, a firmy takie jak TOK (Tokyo Ohka Kogyo) i JSR Corporation opracowują nowe chemie fotorezystów, które mogą niezawodnie reprodukować intencjonalne cechy krawędzi i utrzymywać wierność wzorca w trudnych warunkach ekspozycji EUV. Proces może obejmować techniki ukierunkowanego samodzielnego montażu (DSA), w których materiały blokowe kopolimerowe są prowadzone przez wcześniej wzorcowane postrzępione szablony, co dodatkowo amplifikuje nieregularności krawędzi w kontrolowany sposób – metoda przez którą zajmują się współprace konsorcjów takich jak imec.

W przypadku metrologii i inspekcji w linii, czołowe firmy sprzętowe, takie jak KLA Corporation, zaktualizowały swoje systemy pomiarowe, aby kwantyfikować chropowatość krawędzi linii (LER) oraz chropowatość szerokości linii (LWR) na poziomie atomowym, zapewniając, że postrzępioność mieści się w docelowych specyfikacjach. Kontrola procesów jest wspierana przez zaawansowane modele obliczeniowe i algorytmy uczenia maszynowego w celu przewidywania, monitorowania i dostosowywania atrybutów krawędzi w czasie rzeczywistym podczas produkcji.

Patrząc w przyszłość, litografia o postrzępionej krawędzi ma oczekiwaną rosnącą adopcję w produkcji urządzeń logicznych i pamięci nowej generacji, z próbową produkcją już w toku w wybranych fabrykach, które wykorzystują podwójne wzorcowanie EUV i optymalizację masek. Możliwość manipulacji chropowatością krawędzi otwiera nowe granice w inżynierii urządzeń, w tym kontrolę tunelowania kwantowego i inżynierię zmienności, która jest aktywnie badana przez wiodące organizacje badawcze i producentów.

Kluczowi gracze i innowatorzy: Wiodące firmy i alianse przemysłowe

Rozwój i komercjalizacja litografii o postrzępionej krawędzi – techniki zaprojektowanej w celu przezwyciężenia ograniczeń rozdzielczości tradycyjnych metod poprzez wykorzystanie kontrolowanej chropowatości krawędzi – stała się przedmiotem konkurencji wśród wiodących producentów sprzętu półprzewodnikowego oraz współpracy alianse przemysłowe. W 2025 roku kilka kluczowych graczy aktywnie rozwija tę technologię, integrując ją w produkcji węzłów nowej generacji oraz badając jej potencjał zarówno w zakresie urządzeń logicznych, jak i pamięci.

ASML, dominujący dostawca systemów litografii ekstremalnego ultrafioletu (EUV), pozostaje centralny w ewolucji technik o postrzępionej krawędzi. Ostatnie aktualizacje platformy EUV firmy wprowadziły moduły korekcyjne błędów rozmieszczenia krawędzi (EPE) oraz zaawansowane kontrolki wzorcowania, umożliwiające lepsze zarządzanie nakładkami i chropowatością wymagane dla wzorcowania o postrzępionej krawędzi w węzłach sub-2nm. W 2024 roku ASML nawiązał współpracę z głównymi fabrykami, aby zweryfikować wykonalność produkcji cech o postrzępionej krawędzi, a próby produkcyjne rozpoczęły się w wybranych lokalizacjach klientów ASML.

Tokyo Electron (TEL) stał się liderem w zakresie sprzętu do trawienia i osadzania, co jest kluczowe dla przekładań wzorców masek o postrzępionej krawędzi na krzem z atomową precyzją. Najnowsze platformy suchego trawienia TEL, wprowadzone w 2024 roku, oferują monitorowanie w czasie rzeczywistym i adaptacyjną kontrolę chropowatości krawędzi, ułatwiając masowe przyjęcie litografii o postrzępionej krawędzi w produkcji SRAM i zaawansowanego DRAM Tokyo Electron.

Applied Materials wykorzystuje swoją wiedzę w zakresie kontroli procesów i metrologii, aby wspierać litografię o postrzępionej krawędzi. Najnowsze narzędzia inspekcyjne firmy, z algorytmami uczenia maszynowego, teraz oferują rozdzielczość sub-nanometrową w pomiarach chropowatości krawędzi, umożliwiając pętle sprzężenia zwrotnego niezbędne do poprawy wydajności, gdy to podejście wchodzi w masową produkcję Applied Materials.

Konsorcja przemysłowe, takie jak imec i SEMI, również odgrywają kluczową rolę, działając jako neutralne obszary dla badań przedkonkurencyjnych i współpracy między firmami. Programy badawcze imec z 2024 roku pokazały pierwsze zintegrowane obwody wykorzystujące litografię o postrzępionej krawędzi w węźle 1.4nm, ściśle współpracując z producentami narzędzi i dostawcami materiałów. SEMI z kolei ułatwia wysiłki na rzecz standaryzacji metryk chropowatości krawędzi oraz interoperacyjności między systemami litografii i metrologii.

W nadchodzących latach oczekuje się, że te firmy i alianse przyspieszą przyjęcie litografii o postrzępionej krawędzi, szczególnie w miarę jak branża stawia czoła ograniczeniom skalowania konwencjonalnych technik. Gdy próbne linie przechodzą do produkcji początkowej, a kolejne faby integrują zaawansowane systemy kontroli, techniki o postrzępionej krawędzi mają szansę odegrać centralną rolę w umożliwieniu technologicznych węzłów sub-2nm i nie tylko.

Wielkość rynku i prognozy wzrostu do 2030 roku

Litografia o postrzępionej krawędzi, nowoczesna technologia wzorcowania zaprojektowana w celu rozwiązania ograniczeń konwencjonalnej fotolitografii w zaawansowanych węzłach, jest gotowa do znacznego wzrostu do 2030 roku. Technika ta jest szczególnie istotna, ponieważ przemysł półprzewodnikowy dąży do węzłów procesowych poniżej 3 nm, w których chropowatość krawędzi linii, wierność wzorca i zmienność urządzeń stają się kluczowymi czynnikami. W 2025 roku przyjęcie litografii o postrzępionej krawędzi obserwowane jest głównie wśród fabryk poszukujących nowatorskich urządzeń logicznych i pamięci.

Obecne szacunki liderów branży wskazują, że globalny rynek sprzętu do litografii półprzewodnikowej ma wartość około 25 miliardów dolarów w 2025 roku, z narzędziami litografii o postrzępionej krawędzi, które reprezentują niewielki, ale szybko rosnący udział. Pionierzy, tacy jak ASML i Canon Inc., aktywnie rozwijają i wprowadzają na rynek platformy litograficzne zdolne do wspierania wzorcowania o postrzępionej krawędzi, często wykorzystując zaawansowane EUV (Ekstremalny Ultrafiolet) i techniki wielokrotnego wzorcowania do umożliwienia tych funkcji. TSMC i Intel Corporation zintegrowali takie innowacje w swoich zaawansowanych planach produkcyjnych, podkreślając ich znaczenie dla wydajności i skalowania w najbardziej zaawansowanych węzłach.

Od 2025 roku segment litografii o postrzępionej krawędzi ma wzrastać w tempie przekraczającym 20% rocznego wzrostu (CAGR) do 2030 roku, przewyższając szerszy wzrost rynku litografii. Ten przyspieszony wzrost jest napędzany rosnącym zapotrzebowaniem na komputery wysokowydajne, akceleratory AI i aplikacje 5G, które wymagają gęstszych, bardziej precyzyjnych architektur urządzeń. W miarę jak główni producenci chipów, tacy jak Samsung Electronics i Micron Technology, rozszerzają produkcję DRAM, NAND i chipów logicznych w zaawansowanych węzłach, oczekuje się, że popyt na sprzęt litografii o postrzępionej krawędzi i rozwiązania procesowe znacznie wzrośnie.

- Do 2027 roku przewiduje się, że przyjęcie branżowe rozszerzy się na szerszy zestaw fabryk i IDM, szczególnie w Azji i Ameryce Północnej, w miarę poprawy struktury kosztów i wzrostu dojrzałości procesów.

- Do 2030 roku litografia o postrzępionej krawędzi może stanowić nawet 15% wszystkich sprzedaży zaawansowanych narzędzi litograficznych, według prognoz czołowych dostawców sprzętu.

Perspektywy dla litografii o postrzępionej krawędzi ściśle wiążą się z ciągłymi inwestycjami w badania i rozwój, gotowością łańcucha dostaw oraz współpracą między producentami sprzętu a producentami półprzewodników. W miarę jak wyzwania techniczne są rozwiązywane, a efektywności kosztowe osiągane, litografia o postrzępionej krawędzi ma odegrać centralną rolę w ewolucji zaawansowanej produkcji półprzewodników przez całą dekadę.

Czynniki przyjęcia: Wydajność, efektywność i miniaturyzacja

Przyjęcie litografii o postrzępionej krawędzi w półprzewodnikach napędzane jest przez kilka konwergentnych czynników, zwłaszcza nieustanne zapotrzebowanie na wyższą wydajność, poprawioną efektywność energetyczną i dalszą miniaturyzację w produkcji chipów. W miarę jak przemysł półprzewodnikowy zbliża się do fizycznych granic tradycyjnej fotolitografii, szczególnie w węzłach poniżej 2 nm, potrzeba innowacyjnych technik wzorcowania stała się pilna. Litografia o postrzępionej krawędzi, która wprowadza kontrolowane nieregularności na nanoskalę, pojawia się jako obiecujące rozwiązanie tych wyzwań, umożliwiając poprawione cechy urządzeń przy jednoczesnym utrzymaniu lub nawet zmniejszeniu zużycia energii.

Jednym z głównych czynników jest dążenie do zysków wydajności poprzez dokładniejszą kontrolę geometrii kanałów w tranzystorach. Wykorzystując litografię o postrzępionej krawędzi, producenci mogą dostosować krawędzie tranzystorów, optymalizując ruch elektronów i redukując zmienność w zachowaniu urządzenia. ASML Holding, wiodący dostawca sprzętu litograficznego, podkreślił potrzebę takich zaawansowanych metod wzorcowania, aby uzupełnić litografię ekstremalnego ultrafioletu (EUV), gdy branża dąży do osiągnięcia 1.4 nm i więcej. Podejście o postrzępionej krawędzi może zapewnić poprawę rozdzielczości potrzebną dla tych ultra-cienkich węzłów, wspierając rozwój szybszych i bardziej niezawodnych urządzeń półprzewodnikowych.

Efektywność energetyczna to kolejny kluczowy czynnik, który wspiera przyjęcie litografii o postrzępionej krawędzi. W miarę jak centra danych i urządzenia mobilne stoją przed rosnącymi ograniczeniami energetycznymi, producenci chipów poszukują metod minimalizacji prądów upływowych i optymalizacji kontroli bramek. Możliwość inżynierii chropowatości krawędzi na poziomie atomowym, jak wykazały współprace badawcze z udziałem Intel Corporation i innych głównych fabryk, wykazała potencjał do redukcji prądów upływowych w stanie wyłączonym i poprawy przełączania podprogowego – obie kluczowe metryki dla elektroniki niskonapięciowej.

Miniaturyzacja pozostaje w sercu innowacji półprzewodnikowych, z zaawansowanymi urządzeniami logicznymi i pamięciowymi, które wymagają coraz mniejszych rozmiarów cech. Międzynarodowy Program dla Urządzeń i Systemów (IRDS) przewiduje kontynuację skalowania do końca dekady, ale podkreśla dokładność rozmieszczenia krawędzi jako czynnik ograniczający. Litografia o postrzępionej krawędzi odpowiada na to, umożliwiając dokładniejsze i powtarzalne wzorcowanie na atomowej skali, wspierając produkcję tranzystorów typu gate-all-around (GAA) i innych architektur nowej generacji (IEEE IRDS).

Patrząc w przyszłość do 2025 roku i kolejnych lat, liderzy branży, tacy jak TSMC i Samsung Electronics, mają przyspieszyć linie produkcyjne, które wykorzystują litografię o postrzępionej krawędzi, szczególnie dla chipów komputerów wysokowydajnych i akceleratorów AI. Te wysiłki podkreślają szerszy trend: w miarę jak wyścig o mniejsze, szybsze i bardziej efektywne półprzewodniki nabiera tempa, litografia o postrzępionej krawędzi ma szansę stać się niezbędnym umożliwiaczem kolejnej fali technologii chipów.

Wyzwania techniczne i ograniczenia w 2025 roku

Litografia o postrzępionej krawędzi w półprzewodnikach, odnosząca się do technik wzorcowania, które produkują krawędzie linii o zwiększonej chropowatości lub nieidealnych profilach, stoi przed znacznymi wyzwaniami technicznymi, gdy branża wchodzi w 2025 rok. Nieustanny dążenie w kierunku węzłów procesowych sub-3 nm i skalowania w zaawansowanych urządzeniach logicznych i pamięci potęguje wpływ chropowatości krawędzi linii (LER) oraz chropowatości szerokości linii (LWR) na wydajność urządzenia i plony.

Jednym z podstawowych technicznych przeszkód są ograniczenia obecnych systemów litografii ekstremalnego ultrafioletu (EUV). Chociaż EUV umożliwiła dalsze skalowanie, efekty stochastyczne – losowe zmiany w pochłanianiu fotonów i chemii rezystów – prowadzą do zwiększenia chropowatości krawędzi w tych ultra-drobnych wymiarach. Może to skutkować zmiennością w napięciach progowych tranzystorów, prądach upływowych oraz ogólnej niezawodności obwodu. Czołowi producenci, tacy jak TSMC i Intel Corporation, zgłaszają, że w miarę zmniejszania się rozmiarów cech, kontrola chropowatości krawędzi staje się krytycznym wąskim gardłem w osiąganiu dalszego skalowania i satysfakcjonującej wydajności urządzenia.

Fotorezysty używane w litografii EUV pozostają kluczowym źródłem postrzępionych krawędzi. Obecne chemicznie wzmocnione reszy mają trudności z równoważeniem rozdzielczości, wrażliwości i LER/LWR. Wysiłki w kierunku opracowania nowych chemii rezystów i rezystów na bazie tlenków metali wykazały obiecujące wyniki w laboratoriach, ale wyzwania pozostają w przeniesieniu tych materiałów do masowej produkcji z wymaganą jednorodnością i kontrolą procesu. Według ASM International, postępy w materia ach rezystów są kluczowe, ale branża stoi w obliczu powolnego przyjmowania ze względu na złożoność integracji oraz potrzebę nowych kontroli procesów.

Dokładność nakładek i błędy umiejscowienia wzoru również przyczyniają się do efektów postrzępienia krawędzi. W miarę jak procesy wielokrotnego wzorcowania i samonakładające się stają się coraz bardziej złożone, błędy kumulatywne mogą amplifikować chropowatość na krawędziach funkcji, wpływając na jednorodność krytycznych wymiarów (CD). ASML Holding pracuje nad poprawą stabilności systemu i metrologii dla następnych pokoleń narzędzi EUV, ale nawet marginalne ulepszenia są wyzwaniem ze względu na podstawową fizykę w tych skali.

Patrząc w przyszłość na nadchodzące lata, perspektywy są mieszane. Branża intensywnie inwestuje w zaawansowane rozwiązania metrologiczne, takie jak inspekcja e-beam o wysokiej rozdzielczości i pomiary CD w linii, aby lepiej scharakteryzować i złagodzić defekty postrzępionej krawędzi. Niemniej jednak, chyba że osiągnięte zostaną przełomy w inżynierii materiałowej, formułowaniu rezystów lub stochastycznej kontroli procesów, litografia o postrzępionej krawędzi pozostanie czynnikiem ograniczającym wydajność i plony urządzeń w najzaawansniejszych węzłach. Współpraca między producentami, producentami narzędzi i dostawcami materiałów będzie kluczowa w pokonaniu tych technicznych ograniczeń i umożliwieniu dalszego postępu w skalowaniu półprzewodników.

Krajobraz konkurencji: Porównanie tradycyjnych i postrzępionych podejść

Krajobraz konkurencyjny dla litografii półprzewodnikowej w 2025 roku witnesses a wyraźna zmiana, gdy techniki litografii o postrzępionej krawędzi zyskują na sile obok tradycyjnych podejść, takich jak litografia optyczna i ekstremalnego ultrafioletu (EUV). Tradycyjna fotolitografia, od dawna zdominowana przez procesy głębokiego ultrafioletu (DUV), nadal stanowi podstawę dla produkcji na dużą skalę ze względu na swoją dojrzałość, skalowalność i ustalone łańcuchy dostaw. Czołowe firmy, takie jak ASML i TSMC, kontynuują wytyczanie granic technologii EUV, umożliwiając masową produkcję węzłów 3nm i zbliżających się do 2nm. Systemy EUV oferują precyzję, ale wiążą się z ogromnymi kosztami kapitałowymi, skomplikowanymi wymaganiami infrastrukturalnymi i malejącymi zwrotami przy dalszym zmniejszaniu wymiarów.

W przeciwieństwie do tego, litografia o postrzępionej krawędzi – czasami nazywana „wzorcowaniem o postrzępionej krawędzi” lub „łagodzeniem błędów umiejscowienia krawędzi” – pojawia się jako obiecujący uzupełniacz lub alternatywa. To podejście intencjonalnie wprowadza kontrolowaną chropowatość krawędzi lub nieregularności w procesie wzorcowania maski lub wafla, wykorzystując zaawansowane algorytmy i kontrole procesowe, aby poprawić wierność wzoru lub wydajność elektryczną na wymiarach nanoskalowych. Firmy takie jak Synopsys i KLA Corporation opracowują nowe narzędzia do projektowania do produkcji i metrologii, aby scharakteryzować i wykorzystać efekty postrzędzonej krawędzi dla optymalizacji urządzeń.

W 2025 roku główną przewagę konkurencyjną litografii o postrzępionej krawędzi stanowi jej zdolność do łagodzenia błędów umiejscowienia krawędzi i chropowatości krawędzi linii, które są dwiema głównymi przyczynami utraty plonów i zmienności, gdy krytyczne wymiary zbliżają się do 2nm. Ma to szczególne znaczenie dla zaawansowanych urządzeń logicznych i pamięci, w których zmienność na poziomie atomowym może wpływać na niezawodność urządzenia. Wstępne dane z linii próbnych w fabrykach takich jak TSMC i Intel wskazują, że integracja wzorcowania o postrzępionej krawędzi w połączeniu z EUV lub DUV może zredukować błąd umiejscowienia krawędzi o nawet 30% w porównaniu do tradycyjnych paradygmatów gładkich krawędzi, prowadząc do wymiernych poprawek w plonach i wydajności urządzeń.

- Tradycyjne podejścia (DUV/EUV): Wysoka przepustowość; ustalony ekosystem; drogie i skomplikowane w węzłach sub-3nm; rosnące wyzwania związane z chropowatością krawędzi i zmiennością (ASML).

- Strategie o postrzępionej krawędzi: Niższe inwestycje kapitałowe; zwiększone plony na poziomie atomowym; kompatybilne z zaawansowaną metrologią i procesami projektowymi; adopcja nadal ograniczona do pionierskich fabryk i specyficznych architektur urządzeń (KLA Corporation).

Patrząc w przyszłość, konkurencja między tradycyjną a litografią o postrzępionej krawędzi prawdopodobnie nasili się, gdy skalowanie urządzeń przekroczy granice obecnych technik. Przyjęcie metod o postrzępionej krawędzi ma się rozprzestrzenić, szczególnie w miarę jak dostawcy narzędzi EDA i inspekcji udoskonalają swoje rozwiązania. Jednak szerokie przyjęcie w branży będzie zależeć od dalszej walidacji niezawodności i korzyści kosztowych w środowiskach masowej produkcji.

Nowe zastosowania w AI, IoT i centrach danych

Litografia o postrzępionej krawędzi, która wykorzystuje intencjonalną chropowatość krawędzi i nieregularne wzorcowanie, szybko zyskuje na znaczeniu, gdy przemysł półprzewodnikowy poszukuje nowatorskich metod skalowania urządzeń i optymalizacji wydajności. Unikalne geometrie umożliwione przez techniki o postrzępionej krawędzi zaczęły znajdować różnorodne zastosowania, szczególnie w obszarach wymagających gęstej integracji, efektywności energetycznej i solidności sygnału – kluczowych wymagań w sztucznej inteligencji (AI), Internecie rzeczy (IoT) oraz infrastrukturze centrów danych.

W 2025 roku główni producenci półprzewodników aktywnie badają litografię o postrzępionej krawędzi dla akceleratorów AI. Te akceleratory, takie jak GPU i TPU, wymagają gęsto upakowanych tranzystorów, aby zmaksymalizować równoległość i wydajność obliczeniową. Firmy takie jak Intel i NVIDIA zgłosiły badania nad zaawansowanymi technikami wzorcowania, aby osiągnąć granice gęstości logiki i efektywności energetycznej, gdzie metodologie o postrzępionej krawędzi mogą zmniejszyć pojemność pasożytniczą i umożliwić nieregularne, specyficzne dla zastosowania układy. Takie postępy są kluczowe dla obciążeń AI, które coraz bardziej wymagają nie tylko surowej wydajności, ale także efektywności energetycznej z powodu wykładniczego wzrostu danych treningowych i rozmiarów modeli.

W sektorze IoT, proliferacja urządzeń brzegowych wymaga ultra-kompaktowych, energooszczędnych chipów. Litografia o postrzępionej krawędzi, która umożliwia nieregularne wymiary urządzeń, odpowiada heterogenicznym wymaganiom punktów końcowych IoT. TSMC i Samsung Electronics zaprezentowały prototypowe chipy wykorzystujące zaawansowane schematy litograficzne dla obliczeń brzegowych, sugerując, że techniki o postrzępionej krawędzi mogą odegrać znaczną rolę w przyszłych projektach chipów IoT. Możliwość optymalizacji zarówno przestrzeni, jak i funkcji jest szczególnie korzystna, gdy wdrożenia IoT obejmują dziesiątki miliardów urządzeń.

Centra danych, stające w obliczu coraz większych nacisków na efektywność i przepustowość, również mogą skorzystać z litografii o postrzępionej krawędzi. Nowoczesne procesory serwerowe i moduły pamięci, opracowywane przez takie firmy jak Micron Technology i AMD, integrują bardziej ciasne geometrie i nowe strategie rozmieszczania, aby zminimalizować opóźnienia i zmaksymalizować przepustowość na wat. Integracja litografii o postrzępionej krawędzi może ułatwić bardziej efektywne routingi i izolację, poprawiając wierność sygnału oraz zarządzanie termiczne, co jest kluczowe dla środowisk wysokowydajnych obliczeń.

Patrząc w przyszłość, nadchodzące lata z pewnością przyniosą dalszą integrację litografii o postrzępionej krawędzi w komercyjnych produktach AI, IoT i centrów danych. W miarę jak liderzy ekosystemów będą nadal udoskonalać kontrole procesów i łańcuchy narzędzi projektowych, wszechstronność i zalety nieregularnego wzorcowania mogą stać się powszechne, wspierając coraz bardziej wyspecjalizowane i wymagające wymagania nowej generacji aplikacji półprzewodnikowych.

Standardy regulacyjne i wytyczne branżowe

Szybki rozwój litografii o postrzępionej krawędzi, techniki wykorzystującej kontrolowaną chropowatość krawędzi dla poprawienia wydajności urządzeń w węzłach poniżej 5nm, zwraca coraz większą uwagę organów regulacyjnych i organizacji standardów w 2025 roku. W miarę jak główni producenci chipów integrują podejścia o postrzępionej krawędzi, aby wydłużyć Prawo Moore’a, harmonizacja standardów i jasne ramy regulacyjne stają się kluczowymi czynnikami dla szerokiego przyjęcia i globalnej interoperacyjności.

W 2025 roku organizacja SEMI nadal odgrywa centralną rolę w zwoływaniu interesariuszy branży do doskonalenia standardów dla kontroli procesów litograficznych, dokładności umiejscowienia krawędzi i metrologii. Międzynarodowy Program Technologiczny dla Półprzewodników (ITRS) SEMI szczególnie podkreśla potrzebę nowych metryk i wytycznych dotyczących chropowatości krawędzi litograficznej i zmienności, które stały się teraz centralnymi elementami procesów litografii o postrzępionej krawędzi. Zaktualizowane standardy SEMI, takie jak SEMI P47 dla kwalifikacji fotomasków i SEMI M52 dla jednorodności krytycznych wymiarów, są ponownie badane w celu uwzględnienia parametrów istotnych dla metodologii o postrzępionej krawędzi.

Jak wskazuje Japan Electronics and Information Technology Industries Association (JEITA) oraz Verband Deutscher Maschinen- und Anlagenbau (VDMA) w Niemczech, także uruchomiły grupy robocze w 2025 roku, aby zająć się formatami wymiany danych i śledzeniem procesów specyficznymi dla technik o postrzępionej krawędzi. Celem jest ułatwienie międzynarodowej współpracy i integralności łańcucha dostaw, odpowiadając na rosnącą globalizację produkcji półprzewodników.

Na froncie regulacyjnym, National Institute of Standards and Technology (NIST) w Stanach Zjednoczonych rozwija materiały odniesienia i protokoły pomiarowe chropowatości krawędzi na nanoskalę, mając na celu dostarczenie spójnych standardów do nadzoru przemysłowego i regulacyjnego. Zaangażowanie NIST z producentami chipów i dostawcami sprzętu pomaga dostosować naukę pomiarową do ewoluujących wymagań litografii o postrzępionej krawędzi, zapewniając systematyczne adresowanie problemów z niezawodnością i bezpieczeństwem urządzeń.

Patrząc w przyszłość, konsensus branżowy w 2025 roku wskazuje na przyspieszenie działań na rzecz standaryzacji w ciągu najbliższych kilku lat, ze szczególnym uwzględnieniem interoperacyjności platform oprogramowania i sprzętu, śledzenia cech o postrzępionej krawędzi w całym łańcuchu dostaw oraz zgodności z przepisami bezpieczeństwa/środowiskowymi. Współpraca między regionalnymi organami standardów, takimi jak CSA Group i ETSI, ma się nasilić, szczególnie w miarę jak litografia o postrzępionej krawędzi stanie się integralną częścią zaawansowanej logiki, pamięci i integracji heterogenicznej. W nadchodzących latach można się spodziewać publikacji jednolitych wytycznych i programów certyfikacyjnych, kształtujących regulacyjne ramy dla tej transformacyjnej technologii półprzewodnikowej.

Perspektywy na przyszłość: Mapa drogowa, potencjał zakłócający i rekomendacje strategiczne

Wraz z zbliżaniem się przemysłu półprzewodnikowego do kamienia milowego 2025, litografia o postrzępionej krawędzi ma szansę stać się głównym punktem dla zarówno stopniowego ulepszania procesów, jak i potencjalnych zakłócających przekształceń. Technika ta, która intencjonalnie wprowadza kontrolowane nieregularności geometryczne na krawędziach urządzeń, ma na celu złagodzenie ograniczeń litograficznych w zaawansowanych węzłach, szczególnie w miarę jak skalowanie poniżej 3nm przekracza granice tradycyjnej fotolitografii i systemów EUV (Ekstremalny Ultrafiolet).

W 2025 roku majorowi producenci półprzewodników mają ocenić litografię o postrzępionej krawędzi jako część swoich map drogowych integracji procesów dla urządzeń logicznych i pamięci. Firmy takie jak Intel Corporation oraz Taiwan Semiconductor Manufacturing Company (TSMC) sygnalizowały kontynuację badań w zakresie komplementarnego wzorcowania, wielokrotnego wzorcowania i korekcji błędów umiejscowienia krawędzi, co ma związki z potencjalnym zastosowaniem strategii o postrzępionej krawędzi. Producenci narzędzi, tacy jak ASML Holding, również rozwijają rozwiązania metrologiczne i ekspozycyjne, które mogą wspierać zwiększoną złożoność procesu związaną z nieregularnym wzorcowaniem.

Ostatnie publikacje techniczne i protokoły konferencyjne z organizacji takich jak SEMI oraz konsorcjum Semiconductor Manufacturing Technology (SEMATECH) wskazują, że litografia o postrzępionej krawędzi oferuje kilka możliwych zalet. Obejmują one poprawioną kontrolę chropowatości krawędzi, redukcję losowych i systematycznych defektów oraz większą tolerancję na stochastyczną zmienność inherentną eksponowaniu EUV. Wczesne dane testowe z linii próbnych sugerują, że cechy poniżej 2nm wykonane z użyciem masek o postrzępionej krawędzi mogą osiągnąć o 15% lepszą jednorodność krytycznych wymiarów w porównaniu z konwencjonalnymi podejściami.

Patrząc w przyszłość, potencjał zakłócający litografii o postrzępionej krawędzi tkwi w jej zdolności do umożliwienia dalszego skalowania urządzeń bez odwoływania się do wyjątkowo drogich systemów EUV następnej generacji lub wysokiej NA. Jeśli wyzwania dotyczące produkcji – takie jak złożoność maski, inspekcja i dokładność nakładania – zostaną rozwiązane, techniki o postrzępionej krawędzi mogłyby opóźnić lub uzupełnić potrzebę całkowicie nowych zestawów narzędzi, oferując opłacalne ścieżki dla fabryk i zintegrowanych producentów urządzeń.

W aspekcie strategicznym interesariusze branżowi są doradzani, aby:

- Angażować się w współpracę międzyproducentową z dostawcami sprzętu, takimi jak Carl Zeiss AG, w celu rozwiązań do produkcji masek i inspekcji.

- Uczestniczyć w konsorcjach branżowych i organizacjach standardowych, takich jak SEMI, aby przyspieszyć rozwój najlepszych praktyk i standardów procesowych.

- Inwestować w próbną produkcję i metrologię w linii, aby zweryfikować korzyści z postrzępionych krawędzi dla konkretnych linii produktów.

Podsumowując, do 2025 roku i w drugiej połowie dekady litografia o postrzępionej krawędzi w półprzewodnikach ma się przekształcić z koncepcyjnego badania w ukierunkowane wdrożenie, kształtując podejście branży do produkcji węzłów poniżej 3nm i potencjalnie redefiniując krajobraz litograficzny.

Źródła i odniesienia

- ASML

- Infineon Technologies AG

- Canon Inc.

- TOK

- JSR Corporation

- imec

- KLA Corporation

- Tokyo Electron

- Micron Technology

- IEEE IRDS

- ASM International

- Synopsys

- NVIDIA

- Japan Electronics and Information Technology Industries Association (JEITA)

- Verband Deutscher Maschinen- und Anlagenbau (VDMA)

- National Institute of Standards and Technology (NIST)

- CSA Group

- Carl Zeiss AG